發布日期:2022-07-14 點擊率:62

LVDS的高速、低功耗和低噪聲特性使其成為電信和網絡設備的背板互連、3G蜂窩電話基站中機架內部的互連、數字視頻接口等應用的理想選擇。除上述優點外,LVDS串行器和解串器(圖1)還為系統設計節省了大量的空間和金錢。采用這種方案可以把互連密度降低5倍,在3G及其它具有大量板卡的通信應用中,節省大量的空間和費用。

使用電容實現LVDS數據連接的交流耦合有很多益處,比如電平轉換、去除共模誤差以及避免輸入電壓故障的發生。本文不僅介紹了電容的適當選型,也為和終端拓撲提供指導,同時也討論了共模故障分析的問題。

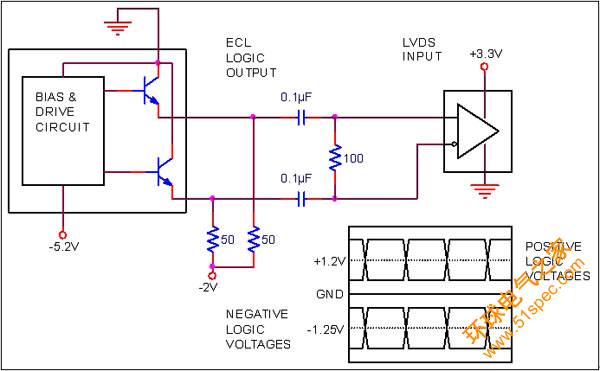

LVDS邏輯輸入是眾多現有邏輯標準的一種。只要信號源可以為LVDS輸入提供足夠的幅度,典型值為差分100mV Vp-p,采用交流耦合就可以提供所需的電平轉換。圖2描述了一個負壓ECL邏輯經交流耦合后將信號轉換到LVDS邏輯的電路圖。

優化共模電壓

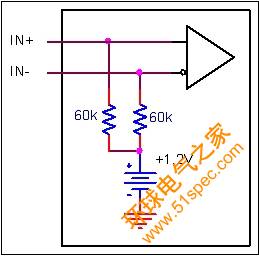

交流耦合LVDS的另外一個優點是允許接收IC設置其最優的共模電壓。圖3展示了一個典型的LVDS輸入電路。一個通常為的內部參考電壓為兩個高阻端接電阻提供偏置。如果輸入是交流耦合,接收IC可以將允許共模電壓設置為內部的偏置電平。

過壓保護

LVDS信號在汽車電子的串行解串器(SerDes)鏈路中總是采用交流耦合,因為這種配置可以防止汽車電池短路。對于任何通過電源配線槽的信號線,一個基本要求是必須能夠忍受與電池電壓短路而不損壞。采用交流耦合的LVDS鏈路,當耦合電容充電到電池電壓時,僅僅會有一個短暫的大電流脈沖。電流的幅度峰值是短路時實際阻抗的函數。電流毛刺的持續時間是耦合電容以及LVDS輸入輸出保護結構的函數。雖然SerDes鏈路在短路時并不工作,但當短路故障解除后可恢復工作。

圖1:串行器-解串器典型應用電路。

圖2:ECL-LVDS電平轉換配置。

圖3:LVDS輸入偏置電路。

圖4:LVDS端接電路。

電容選擇

有以下幾個因素影響到電容的選擇。

1.參數值

LVDS鏈路交流耦合電容的選擇與一系列的參數相關,包括:輸出驅動電平、輸入門限電平、負載阻抗、電纜長度、最長的脈沖周期。

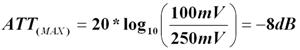

標準的LVDS輸出驅動電平通常定義為最小250mV,且輸入電平門限定義為最大100mV。因此,確保有效電平值的最大的衰減量為:

換句話說,由直流電阻產生的衰減、交流衰減以及電容耦合衰減的總合必須小于8dB。兩端差分負載阻抗通常為100Ω,分析電纜長度時需要同時考慮電纜的交流和直流衰減以及連接器阻抗導致的衰減。最后,還必須考慮數據本身,LVDS連接可以傳輸的最大脈沖寬度取決于工作頻率和數據傳輸協議對連續1(或0)的數量限制。

對于具體應用,精確的計算可能過于棘手,也可以簡單選用電容,能夠滿足大多數應用的要求。當數據速率降到10MHz以下或采用更長的電纜時(例如>5米),需要重新核實電容值,也可以通過計算、仿真或實際測量獲取電容值。

2.電壓和介質

電容的工作電壓應遠大于出現故障狀況時的最大峰值電壓。在汽車電子應用中,峰值故障電壓是18V。一般不需要將故障條件下的電壓加倍,例如:將電池電壓加倍或考慮甩負載電壓。

使用X5R、X7R或類似介質的電容,避免使用那些電壓或溫度系數有明顯變化的介質電容,如Y5V或Z5U。

端接拓撲

端接拓撲可以從三個主要電路中選擇:(1)純差分,(2)中心抽頭差分,(3)戴維寧端接。圖3給出了這三個電路,純差分是最常用的配置,且在良好屏蔽環境中用于信號端接可以提供很好的工作性能。中心抽頭的差分端子將100Ω分為兩個50Ω電阻,且在中心抽頭位置使用旁路電容。由于任何耦合到LVDS線對上的共模能量對地都有一個低阻通路,這種方式在噪聲環境下工作很好。純差分和中心抽頭差分端接必須用于包含內部偏置的LVDS輸入電路。

如果LVDS接收器不提供內部偏置,且輸入信號為交流耦合,則必須使用戴維寧端接。所選電阻必須使每條線上的戴維寧等效電阻為50Ω,且每條線的戴維寧等效電壓為,圖5數值工作于電源。

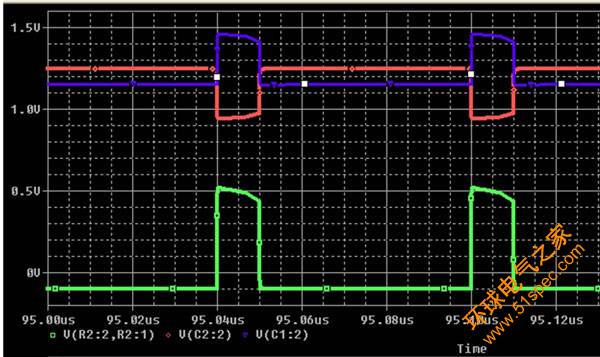

圖5:非直流平衡的交流耦合LVDS連接。

交流耦合鏈路故障排查

通過交流耦合的LVDS鏈路傳輸數據必須是直流平衡,這意味著所傳輸的0和1的數目接近相等。具有50%占空比的時鐘信號本身就是直流平衡。很多數據編碼算法,如曼徹斯特編碼,也提供直流平衡數據流。圖5展示了一個非直流平衡連接的波形。

圖5中上部的曲線(紅色和藍色)反映了20%占空比碼流的單端測量結果。下部曲線(綠色)是一個互補和真實信號的差分測量結果。差分測量結果不以0V位置為中心。仔細分析顯示,每一半波形的面積相等。交流耦合連接無法傳輸任何直流電流,這種情況下,負端偏移恰恰小于100 mV,滿足不了LVDS最小輸入電平的要求。

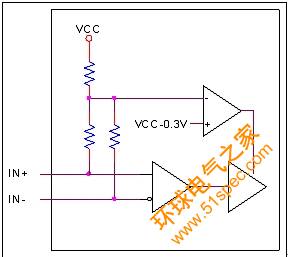

輸入故障檢測

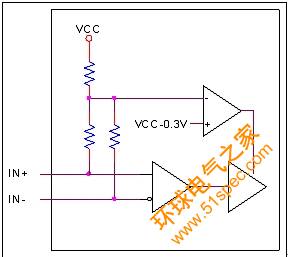

一些LVDS器件在其輸入端帶有故障檢測電路。故障檢測電路用于識別輸入故障,假如檢測到故障則關閉輸出驅動器,圖6給出了一個典型電路。假如交流耦合LVDS連接用在該電路中,戴維寧輸入端接方式是必須的。不采用這種方式會使輸入端的電壓幾乎等于VCC,這將超出LVDS器件的共模電壓范圍。

圖6:LVDS故障檢測電路。

作者:

John Guy

應用工程經理

美信公司