1 引言

隨著數據寬帶網絡的迅猛發展,需要不斷提高系統設備的業務容量。目前的趨勢是采用高速串行通信技術,即采用串行解串器SERDES,把低速的并行數據轉換為高速串行數據連接。SERDES串行接口可在背板或電纜/光纖等不同互聯介質上傳輸高速信號,在提高系統傳輸帶寬的同時,有利于印刷電路板(PCB)布線,并降低系統功耗和噪聲。

TI(德州儀器)推出一系列高性能的通用SERDES,滿足高帶寬、高性能的應用要求,廣泛應用在WI系統、接入設備、傳送網絡、數據通信等通信產品,以及工業控制系統。本文以TLK3132為例,詳細介紹了SERDES工作原理和器件特點,并以WI系統中的CPRI應用需求為例,提供TLK3132的設計方法等。

2 TLK3132工作原理

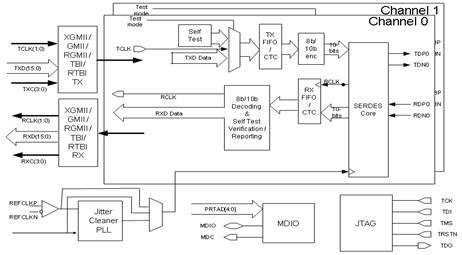

TLK3132是TI推出的一款通用兩通道串行器/解串器(SERDES),采用90nm工藝,能滿足一些低功耗的應用需求,內部功能模塊如圖1所示。SERDES Core的發送部分用于實現8位、9位或10位寬字的并串轉換,然后通過一根電纜或印刷板(PCB)走線發送出去,而接收部分則將串行數據進行串并轉換為8位、9位或10位寬的并行字。

圖1 TLK3132內部功能框圖

下面詳細介紹了6個功能模塊及其應用特點:并行接口、串行接口、時鐘分布電路、8B/10B編解碼電路、PRBS測試以及相關寄存器訪問控制接口MDIO。

2.1 并行接口

TLK3132器件每個通道并行收發側分別包含8位數據位和兩位靈活的控制位,支持各種通用的并行接口,如千兆以太網的介質無關接口RGMII、GMII、RTBI、TBI,以及RNBI、NBI、REBI、EBI、TBID和NBID等多種工作模式。對于DDR模式而言,既支持位邊沿采樣(采樣時鐘邊沿與數據位翻轉邊沿同步),也可支持位中間采樣(采樣時鐘邊沿處于數據位的中間位置);對于SDR模式而言,既支持上升沿采樣并行口數據,也支持下降沿采樣數據。由于使用同步時鐘,在布線時時鐘線和數據線必須等長且時鐘線盡量不要分叉,此外通過配置不同的數據采樣邊沿,可以降低系統互連設計的風險,提高系統設計的魯棒性。

并行接口采用單端的HSTL Class1電平接口,遵循EIA/JESD8-6標準電氣指標規格,同時支持1.5V或1.8V的電源電壓。為了提高HSTL高速接口的SI性能,TLK3132并行接收側集成了可寄存器配置的匹配電阻,采用戴維南等效電路匹配方式,等效于加一個匹配電阻到VDDQ/2,同時也可關閉內部的阻抗匹配電路,如圖2所示;并行發送側可通過寄存器配置4種不同的邊沿速率。

圖2 并行口等效框圖

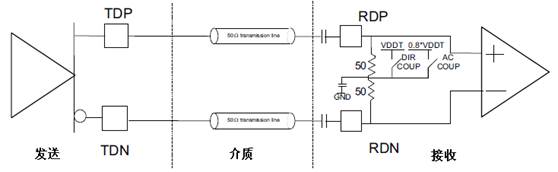

2.2 串行接口

TLK3132支持的串行接口速率從600Mbps到3.75Gbps,不同通道可獨立地工作于全速率、半速率以及1/4速率模式。為了補償高速信號傳輸的介電損耗和趨膚效應,TLK3132高速串行接口發送端具有強大的去加重能力,共支持15級調節能力(達到10.87dB補償),同時支持8級的輸出擺幅設置(從125mV到1375mV);接收端包含有自適應均衡器,最大補償能力得到12dB以上,保證高速串行接口的SI性能。在3.072Gbps速率下可支持50inches的FR4傳輸或30m的電纜傳輸(特性阻抗50歐姆),解決了高速信號在背板側或前基板的設計難題。

圖3是TLK3132高速串行接口的AC耦合框圖,采用CML高速電平接口,發送側內部集成了50歐姆的匹配電阻。接收端支持DC和AC耦合,若采用直流耦合時,共模電壓由發送側決定,匹配電阻直接上拉到VDDT,若采用交流耦合,為得到最優的共模偏置電壓,選擇芯片內部0.8VDDT的偏置電壓。在實際電路設計中,推薦采用交流耦合方式,容易實現不同接口的電平轉換,并可去除共模噪聲,避免外界噪聲對接收端的影響。

圖3 串行接口AC耦合

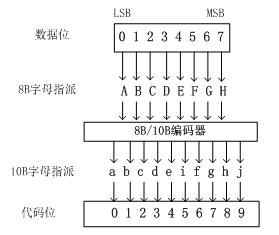

2.3 8B/10B編解碼及通道同步

在串行鏈路通信中,為了實現信號時鐘的恢復,需要避免出現長串0和長串1,同時保持電路上正負電平平衡,能正確地交流耦合避免信號失真,需要傳輸信號中的0和1數量數目相等,因此業界廣泛應用8B/10B編解碼方法:實現8B到10B的映射(圖4),即一個字節(8bits)用10bits來表示,從中挑選出連續0或者1個數不會超過3個,0和1的個數差不大于2 (最多6個’0’或’1’)。

為了實現信號流中0和1的個數相等,在設計編碼時,針對每個原碼設計了兩個編碼,如:十六進制字節0x3B,對應兩個編碼分別為110110 1001(1的個數多于0)和001001 1001(0的個數多于1),在發送過程中不斷統計當前數據流中0和1的個數差,如果0的個數大于1的個數,則發送0X3B字節時取前面一種編碼;反之,則取后面一種編碼,這樣就不斷平衡數據流中0和1的個數,保持串行數據中0和1的數量相同。

圖 4 8B/10B映射

串行通信中,除了有效數據外,還需要一些控制字符傳送某些控制協議。因此,在8B/10編碼中,包含下面兩種信息:

1)D分組,用于傳遞有效業務數據;

2)K分組,用于傳遞控制信息等,如K28.5控制字符10B編碼包含0011111010或1100000101(連續5個’1’或’0’,稱為Comma,千兆以太網使用的8B/10B編碼方案中Comma是唯一的),用于定位串行數據流中每10個bits組的邊界,避免數據流出現錯誤時無法界定每10bit的邊界,導致鏈路中斷。

TLK3132內部兼容了IEEE802.3-2005中關于1000BASE-X物理編碼子層(PCS)技術(注:不支持自協商功能),如CTC FIFO、8B/10B編解碼電路等模塊,同時這些模塊設計時非常靈活,通過MDIO口進行寄存器設置可以使能或關閉。此外,TLK3132通過檢測Comma進行通道同步判斷,內部的狀態機也是參考1000BASE-X規定的鏈路同步和鏈路失步建立機制,因此TLK3132能被廣泛應用在WI、數據網絡、以太網等不同領域。

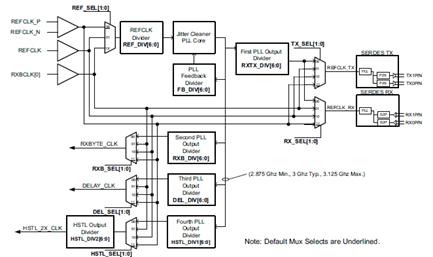

2.4 時鐘電路

SERDES實現的一個關鍵技術是時鐘的產生和分布,圖5是TLK3132芯片內部的時鐘架構。時鐘配置非常靈活,支持單端或差分參考時鐘輸入,同時包括多個高頻鎖相環電路:

1)高速SERDES Core包含了一個高頻倍頻器(用于產生高速串行數據)和一個基于相位內插的CDR(在接收端用于從串行數據中恢復時鐘)。

2)由于串并模塊里的高頻倍頻器環路帶寬很大,最大可達30MHz左右。故TLK3132內部集成了一顆基于LC振蕩器的抖動濾除鎖相環,環路帶寬通常設置在幾百KHz以內,可以對輸入參考時鐘進行濾除,降低參考時鐘對幾百KHz 以上抖動性能的要求,圖6是TLK3132發送鏈路在抖動濾除器打開和關閉下的環路傳遞函數。此外,抖動濾除器也可對鏈路恢復的時鐘(只可接收CH0通道的恢復時鐘RXBCLK(0))進行抖動濾除,提高恢復時鐘的信號質量。

3)PLL1、PLL2、PLL3和PLL4作為倍頻器,和前級抖動濾除鎖相環電路配合,分別產生適合的時鐘頻率以滿足系統各個模塊的需求。

圖5 內部時鐘架構

圖6 TLK3132內部鎖相環環路帶寬

2.5 PRBS測試

TLK3132支持PRBS碼的產生和驗證,便于系統定位鏈路故障,提高設備的可維護性。TLK3132內部有兩套PRBS測試方法,一個在SERDES Core內部(通過寄存器0x9011/0x9012配置),該測試一般是只針對生產測試,且控制性能受限,在電路設計中一般不用該功能;另一個是SERDES Core外面(圖1所示),支持 PRBS測試多項式是

PRBS測試多項式是 ,可以通過寄存器配置(0x10)或外部引腳PRBSEN邏輯控制打開或關閉。此外,PRBS驗證時可通過GPO[1:0]管腳監控PRBS測試誤碼情況,也可訪問寄存器0x1D讀取誤碼數(當讀取該寄存器后,將從新開始誤碼計數)。

,可以通過寄存器配置(0x10)或外部引腳PRBSEN邏輯控制打開或關閉。此外,PRBS驗證時可通過GPO[1:0]管腳監控PRBS測試誤碼情況,也可訪問寄存器0x1D讀取誤碼數(當讀取該寄存器后,將從新開始誤碼計數)。

2.6 MDIO接口和寄存器訪問

TLK3132內部寄存器訪問通過MDIO管理接口實現(遵循IEEE 802.3 Clause 22規格),包括管理數據時鐘(MDC)和管理數據輸入輸出(MDIO)。由于Clause 22直接尋址寄存器空間限制,TLK3132增加了一些擴展寄存器,故支持兩種尋址方式:

1) 直接尋址:主要包括與物理層相關的鏈路配置,地址空間分布在0x00~0x1F,PA[0]的高低電平決定對TLK3132的CH0通道或CH1通道進行操作;

2) 間接尋址:TLK3132的一些擴展功能訪問,如內部時鐘配置、I/O性能配置等。地址空間分布在0x9000~0x9900,不同通道的功能有獨立的寄存器進行配置。通過間接地址訪問寄存器,需要先把寄存器地址寫到0x1E地址,然后把相應的控制字寫到0x1F地址或從0x1F地址讀取相應的寄存器值。

3 TLK3132在CPRI接口的應用

為了處理射頻模塊拉遠技術中基帶單元和射頻單元的光纖鏈接,國際上成立兩個標準化組織:一個是CPRI (Common Public Radio Interface),在2003年由華為、愛立信、NEC、西門子和北電發起成立的組織,致力于基帶、射頻接口的標準化;另一個是OBSAI (Open Base Station Architecture Initiative),由諾基亞、LG電子、三星電子等成立的聯盟。二者都定義了使基帶和射頻分離的標準化接口,也就是將宏基站分為基帶單元BBU和遠端射頻單元RRU兩部分,BBU和RRU之間傳送I/Q數據和控制管理數據,其信號格式就是CPRI或者OBSAI所定義的標準接口。本文以CPRI接口為例,詳解TLK3132在射頻模塊拉遠技術中的應用。

3.1 CPRI接口

CPRI接口在傳輸用戶界面定義了物理層layer1和數據鏈路層layer2兩層協議。在物理層中,將上層接入點的數據進行串并/并串轉換,以及物理層的編解碼(CPRI接口推薦采用8B/10B,遵循IEEE 802.3 2005 Clause36建議);在數據鏈路層,對上層接入點的I/Q數據、物理層協議數據、網絡協議數據(包括以太網數據、高層數據鏈路協議數據)和廠家自定義的控制信息等進行相應的處理。

目前CPRI有三種建議的鏈路速率,分別是614.4Mbps、1228.8Mbps、2457.6Mbp。在發送側,把I/Q數據、控制協議信息、同步信息等復用為CPRI幀結構信息,經過物理層的8B/10B編碼后,通過光纖長距離傳播(幾公里到幾十公里);在接收側,CPRI幀信號經過串并轉換后經過8B/10解碼成相應的I/Q數據和控制協議信息,交由上層數據鏈路處理。

CPRI幀分成基本幀單元和超幀單元。基本幀單元的幀頻是3.84MHz,包括16個字(表示為W=0…15,其中W0為控制字,后15個字為I/Q數據),根據不同的鏈路速率,字的長度分別為8bits、16bits(如圖7所示)、32bits。超幀單元是由256個基本幀單元組成,其中,第1個基本幀單元里的控制字寫入K28.5標志作為超幀的同步控制信息,其余的255個基本幀單元里的控制字包含控制和管理字(C&M)、廠商自定義控制字等,并預留一些控制字。

圖7 線速率1228.8Mbps的CPRI基本幀結構

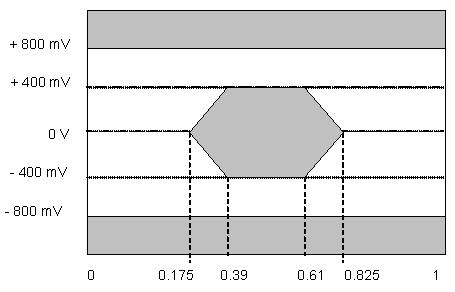

在高速數據鏈路通信中,抖動指標是非常關鍵的,CPRI接口相應推薦了高速串行信號的眼圖和抖動規格。在SERDES發送側,CPRI要求的眼圖模板如圖8所示。

圖8 CPRI接口發送輸出眼圖模板(E.x.LV)

表1 E.6.LV, E.12.LV and E.24.LV發送器AC定時規格(參考資料CPRI Specification V2.0)

|

特性

|

符號

|

范圍

|

單位

|

注釋

|

|

Min

|

Max

|

|

輸出電壓

|

Vo

|

-0.40

|

2.30

|

Volts

|

|

|

差分輸出電壓

|

VDIFFPP

|

800

|

1600

|

mV,p-p

|

|

|

確定性抖動

|

JD

|

|

0.17

|

UI

|

|

|

總抖動

|

JT

|

|

0.35

|

UI

|

|

|

單位間隔 E.6.LV

|

UI

|

1/614.4

|

1/614.4

|

ms

|

+/- 100 ppm

|

|

單位間隔 E.12.LV

|

UI

|

1/1228.8

|

1/1228.8

|

ms

|

+/- 100 ppm

|

|

單位間隔 E.24.LV

|

UI

|

1/2457.6

|

1/2457.6

|

ms

|

+/- 100 ppm

|

在CPRI接口的實現中,TLK3132完成高性能的串/并、并/串轉換,以及CPRI幀的同步和8B/10B編解碼,即CPRI接口物理層的相關功能實現。

3.2 應用例子

根據前面關于TLK3132的器件特點分析和CPRI接口介紹,TLK3132可以很好地滿足CPRI接口的應用要求,圖8是TLK3132在CPRI鏈路中的一個典型功能框圖:TLK3132接收來自光電轉換后的高速串行電信號,經串并轉換后,提取相應控制字符和有效字符并進行8B/10B解碼,送給ASIC或FPGA進行CPRI解幀處理;同時,也接收來自ASIC/FPGA的CPRI幀信號,進行相應的8B/10B編碼后送給SERDES Core完成并串轉換。

在該電路中,TLK3132恢復時鐘送給PLL作為參考時鐘,同時其參考時鐘又來自PLL的輸出時鐘。為保證內部CDR可靠工作,TLK3132要求參考時鐘跟輸入高速串行數據的頻偏控制在+/-200PPM以內,因此外圍PLL在失鎖情況下,必須保證本地振蕩器的自由振蕩頻率要足夠穩定,通常建議采用基于壓控晶振的時鐘方案。

圖8 TLK3132在CPRI接口的典型應用

下面例子說明如何通過MDIO設置TLK3132相關寄存器的軟件配置。假設:CH0和CH1通道串行速率分別為1228.8Mbps和2457.6Mbps、并行接口采用SDR接口并工作在NBI模式、使能內部8B/10B編解碼器、差分參考輸入122.888MHz時鐘,內部抖動濾除鎖相環關閉,則在TI的TLK3132評估板上參考軟件配置如下。

START

CLAUSE 22 //選擇CLAUSE 22模式

SETPHYADD(00) //選擇物理地址0

WRITE(00, 8000) //軟件復位芯片,即對所有寄存器進行復位

READ(11, 3590, FFFF) // 驗證MDIO 功能是否正常

WRITE(1E, 9100) //把0x3FF0寫入0x9100寄存器,差分參考輸入作為SERDES Core的參考時鐘

WRITE(1F, 3FF0)

WRITE(1E, 9000) //高頻倍頻器的倍頻系數設為10

WRITE(1F, 1515)

WRITE(1E, 9001) //設置CH0為1/2速—1228.8Mbps、CH1為全速—2457.6Mbps

WRITE(1F, 6060)

WRITE(10, 8400) //并行接收時鐘選擇各自通道的恢復時鐘

WRITE(11, B197) //并口為SDR且工作在NBI模式、上升沿打數據、8B/10B使能

WRITE(1E, 9002) //設置CH0通道接收為交流耦合、自適應均衡

WRITE(1F, 1005)

WRITE(1E, 9004) //設置CH1通道接收為交流耦合、自適應均衡

WRITE(1F, 1005)

WRITE(1E, 900A) //設置CH0通道串行發送端的擺幅為1000mV,去加重為9.52% (0.87dB)

WRITE(1F, 0B21)

WRITE(1E, 900C) //設置CH1通道串行發送端的擺幅為1000mV,去加重為9.52% (0.87dB)

WRITE(1F, 0B21)

WRITE(10, 8C00) //數據通道復位

PAUSE(100) //等待芯片配置生效

WRITE(1E, 901B) //檢查SERDES Core內部鎖相環是否鎖定

READ(1F, 0011, 0011)

STOP

3.3 實驗測試

由于串行口速率高達1228.8Mbps和2457.6Mbps,對PCB的layout提出較大的挑戰。同時TLK3132具有非常優秀的損耗補償能力,可以調整最佳的去加重補償等級,以得到最佳的信號完整性性能。

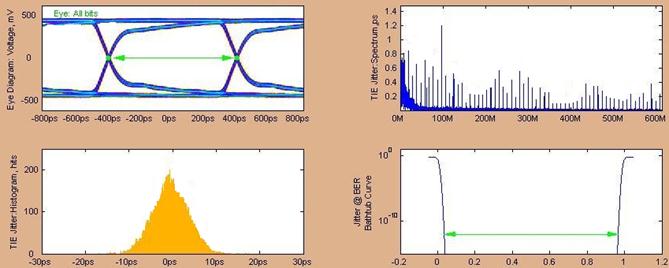

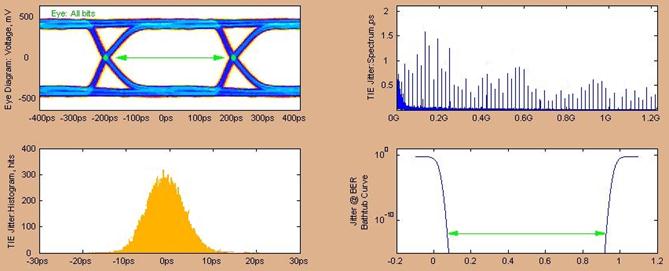

在3.2節的例子中,反復發送K28.5字節數據,實際測試到的TLK3132發送端眼圖如圖9和圖10(分別對應的串行速率為1228.8Mbps和2457.6Mbps),抖動主要來源于隨機噪聲,眼寬均在0.9UI以上,具有非常優越的抖動性能(通過適當調整去加重能力補償傳輸線FR4的損耗,以提高SI性能)。

圖9 1228.8Mbps發送側眼圖(經5inches FR4走線,調整了最優的去加重補償)

圖10 2457.6Mbps發送側眼圖(經5inches FR4走線,調整了最優去加重補償)

4 總結

TLK3132是一款低功耗、低抖動、低成本、高性能的多速率收發器,靈活的內部模塊配置功能使其廣泛地應用于高速串行通信。

為了降低無線網絡的組網成本和提高覆蓋范圍,射頻拉遠技術廣泛應用在3G網絡建設,可把原基站內的基帶單元和射頻單元通過標準化接口(如CPRI等)進行分離,達到一處機房多處天線配置的網絡布局,以減少運營商對固定機房的投資。作為CPRI接口實現的一個關鍵技術—高速串并/并串收發器,TLK3132提供非常優越的SI性能、標準的8B/10B和通道同步處理、靈活的片內時鐘產生和分布等,完全能滿足高可靠、多速率的CPRI接口標準要求。

PRBS測試多項式是

PRBS測試多項式是 ,可以通過寄存器配置(0x10)或外部引腳PRBSEN邏輯控制打開或關閉。此外,PRBS驗證時可通過GPO[1:0]管腳監控PRBS測試誤碼情況,也可訪問寄存器0x1D讀取誤碼數(當讀取該寄存器后,將從新開始誤碼計數)。

,可以通過寄存器配置(0x10)或外部引腳PRBSEN邏輯控制打開或關閉。此外,PRBS驗證時可通過GPO[1:0]管腳監控PRBS測試誤碼情況,也可訪問寄存器0x1D讀取誤碼數(當讀取該寄存器后,將從新開始誤碼計數)。