當前位置: 首頁 > 工業電子產品 > 其他電子產品 > 開發板,套件,編程器 > 開發板

發布日期:2022-10-14 點擊率:65

在當今高速PCB設計中,一組走線的等長越來越重要。Allegro為工程師提供了功能強大的Constrain Manager,即約束管理器,工程師可以很方便地進行各種規則的設定,包括等長規則。 在無線時代早前發表的《DDR布線規則與過程》一文中,已經給出了一種設置等長規則的方法,但這種方法具有一定的局限性,一旦某條網絡的拓補不符合規律,將出現異常。本文以朋友設計的EMMC小卡為例,給出一種相對通用的等長規則設置方法,希望對讀者有幫助。

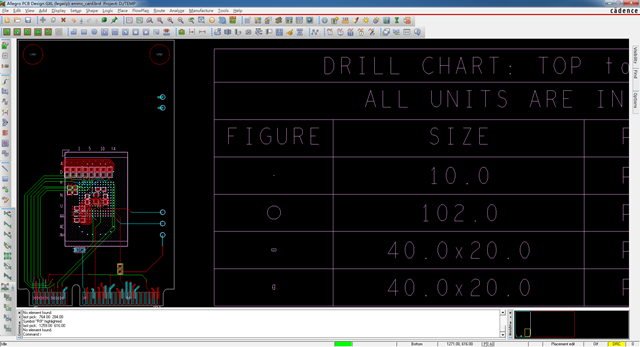

1. 本例中需要實現PCI-e金手指到EMMC芯片等長,包括D0-D7,CLK,CMD這10條網絡。查看各條網絡,確認是否存在串聯匹配電阻。本例中,僅在時鐘線上存在,如下圖的高亮器件。

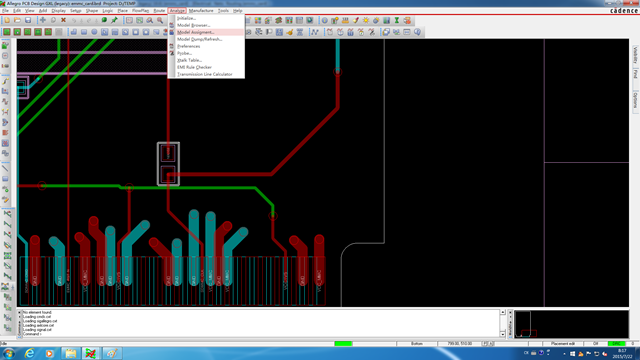

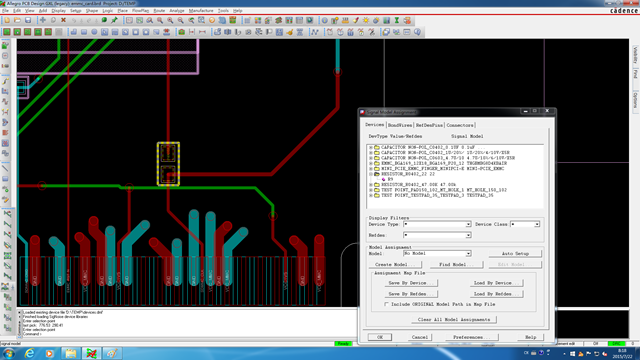

2. 為串聯匹配電阻分配仿真模型,這樣做的目的只有一個:建立Xnet。因為我們要實現的是金手指到達EMMC芯片的引腳等長,所以必須將串聯匹配電阻的兩端網絡視為同一條。點擊Analyze—>Model Assignment,如下圖,

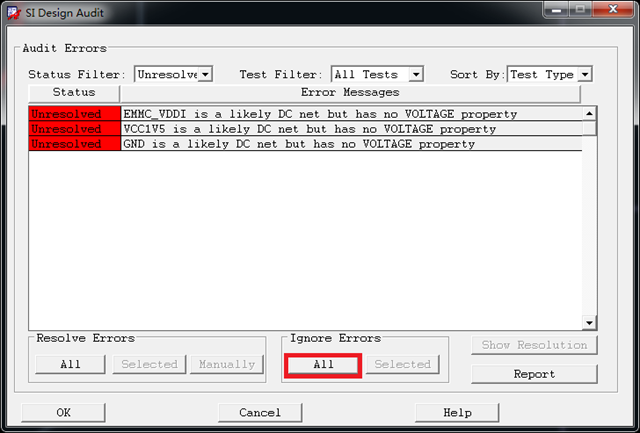

3. 在16.6版本中會彈出一個對話框,就是一些設計錯誤,直接點擊Ignore Errors下面的“All”,然后再點擊“OK”即可,如下圖。

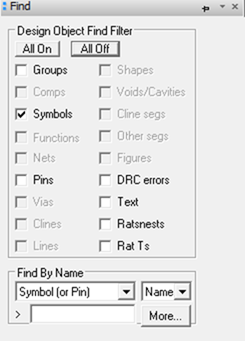

4. 勾選右側Find窗口中的Symbols,如下圖。

5. 點擊時鐘線上的串聯匹配電阻R9,會出現Signal Model Assignment的界面,如下圖。

6. 點擊“Create Model,如下圖。

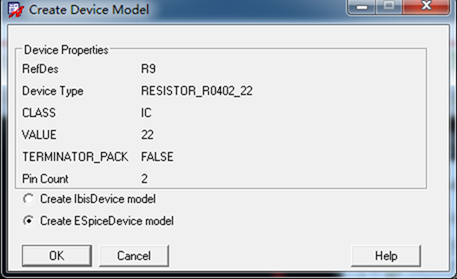

7. 在彈出的Create Device Model對話框中點擊“OK”,如下圖。

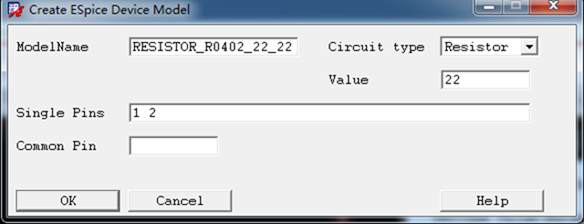

8. 在彈出的Create ESpice Device Model對話框中點擊“OK”,如下圖。

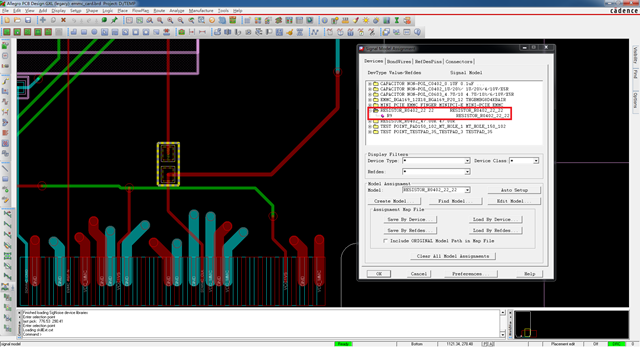

9. 此時返回Signal Model Assignment界面,發現R9已具備Model,如下圖。

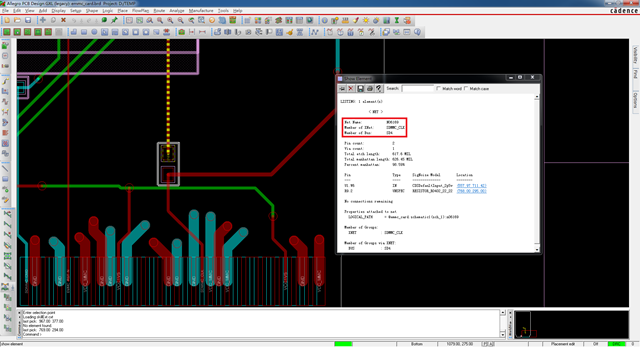

10. 點擊Show Element快捷按鈕,選中EMMC CLK網絡,發現已具備Xnet,如下圖。

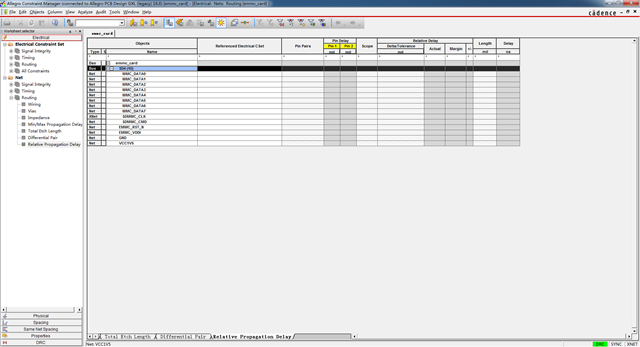

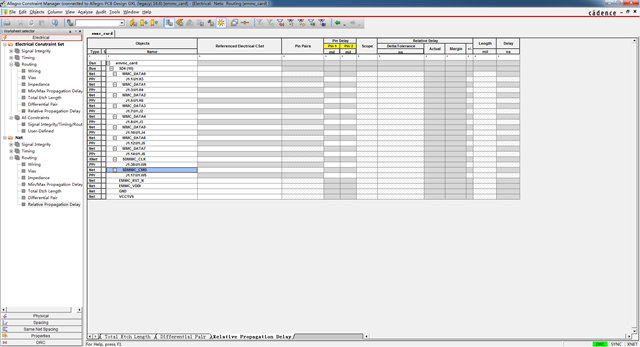

11. 接下來就是創建Match Group,即等長組。點擊Constrain Manager圖標,在彈出的Constrain Manager界面中,點擊左側的Electrical類別下的Relative Propagation Delay,右側出現相對傳輸延遲規則,可以看到EMMC CLK網絡作為Xnet出現在其中,如下圖。

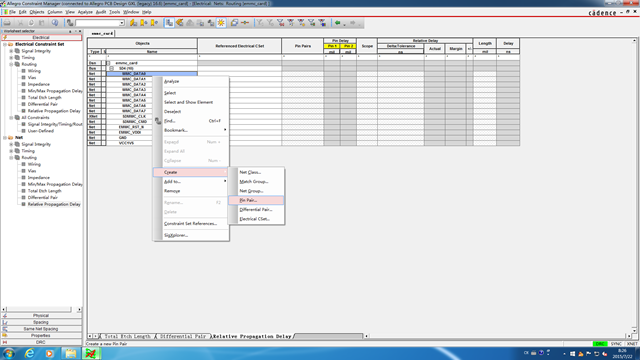

12. 在進行這步操作之前, 筆者再次強調我們要實現金手指到EMMC芯片引腳的等長,即pin到pin的等長,每條網絡可以視為一對Pin Pair。在任意一條網絡上點擊右鍵Create Pin Pair,如下圖。

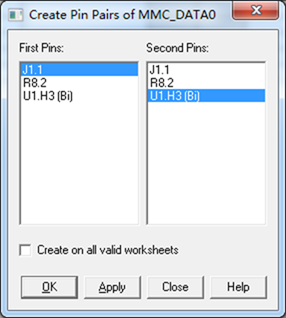

13. 在彈出的Create Pin Pairs of MMC_DATA0對話框中分別選擇需要等長的pin,然后點擊OK,如下圖。當然,我們選擇金手指(J1)和EMMC芯片(U1)的引腳,而不是上拉電阻(R8)。

14. 依次處理所有需要等長的網絡,完成后如下圖所示。

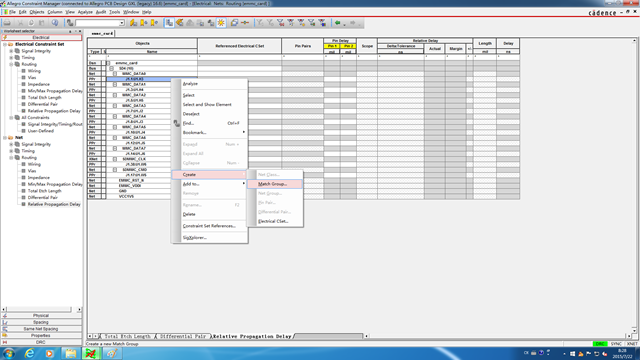

15. 在任意一對pin pairs上點擊右鍵—>Create—>Match Group,如下圖。

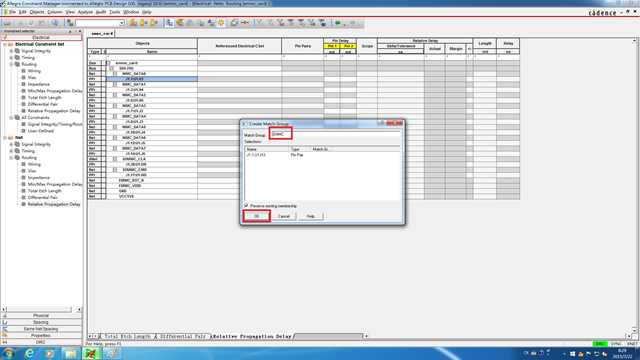

16. 在彈出的對話框中輸入名稱EMMC,然后點擊OK,如下圖。

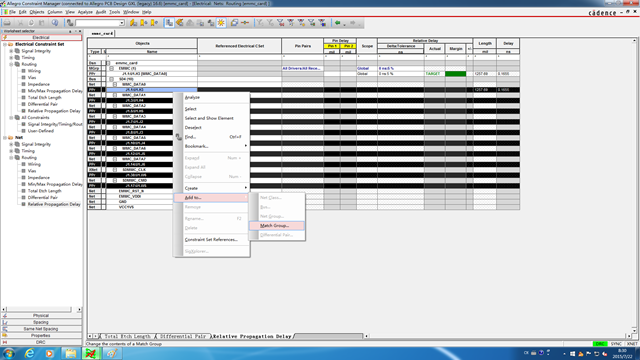

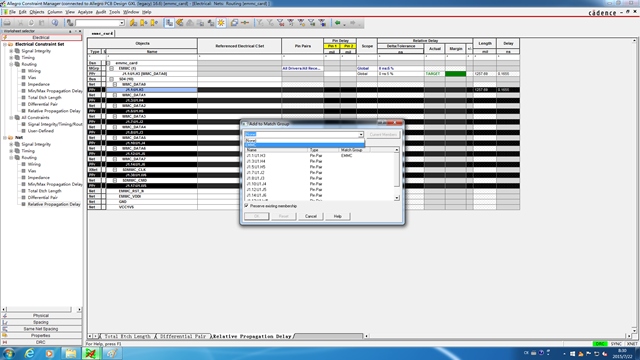

17. 按住Ctrl,依次選擇需要等長的pin pair,然后點擊右鍵—>Add to—>Match Group,如下圖。

18. 在彈出的對話框中點擊下拉箭頭選擇剛剛創建的EMMC,如下圖。

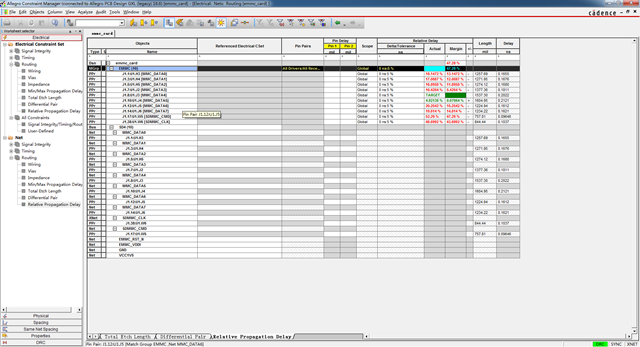

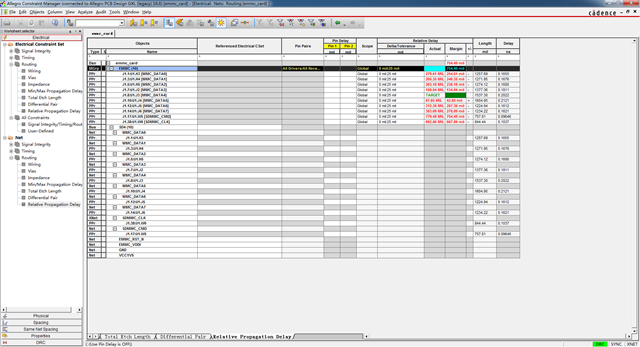

19. 回到Constrain Manager界面,可以看到Match Group已正確建立,如下圖。

20. 但默認是以時間做等長單位,不符合一般習慣,改為mil。點擊“ns”,在彈出的對話框中選擇“mil”,如下圖。

21. 在MGrp中的EMMC名稱所在一行與Delta:Tolerance所在一列的交叉位置輸入等長條件“0:25”,即Delta為0,Tolerance為25,此時看到已變成mil單位,如下圖。

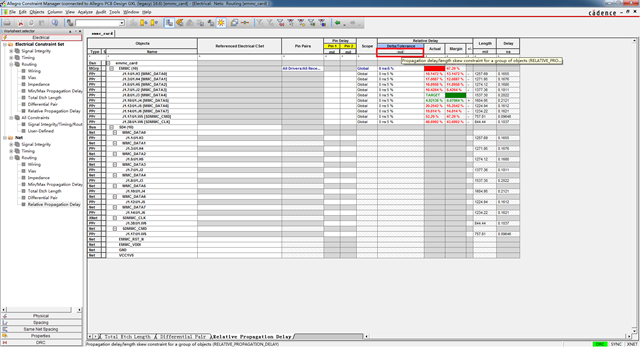

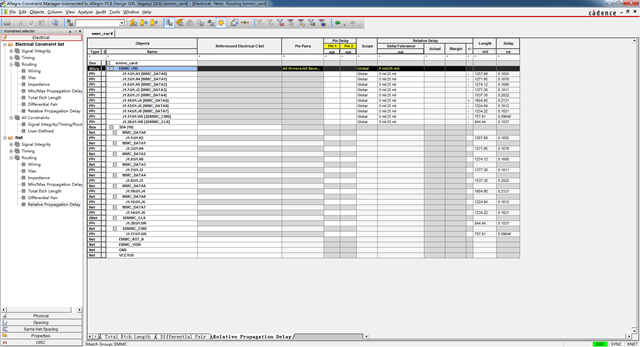

22. 在MGrp中的EMMC名稱上面點擊右鍵—>Analyze,看到當前的等長狀態。

至此,EMMC等長設置完成,接下來就是繞等長了,不是本文討論的內容。本文的核心思想是使用Pin Piars建立等長規則,這種方法相對通用,在Allegro中應用廣泛。在這些年使用Allegro進行PCB設計的 過程中,感受很深的一點就是:如果想很好地掌握Allegro,就必須多思考,多練習,舉一反三。

下一篇: PLC、DCS、FCS三大控

上一篇: 調節PMIC MMPF0100的