在PCB設(shè)計過程中,EDA工程師常常需要匹配兩代PCB的結(jié)構(gòu),這種情況下,將上一代PCB的Outline(板框)導(dǎo)入新的PCB設(shè)計文件中,就可以大大縮短時間,而且尺寸完全準(zhǔn)確。我看到常常有網(wǎng)友檢索類似的信息,所以打算圖文并茂的方式為讀者講解Allegro中導(dǎo)入Outline的方法。

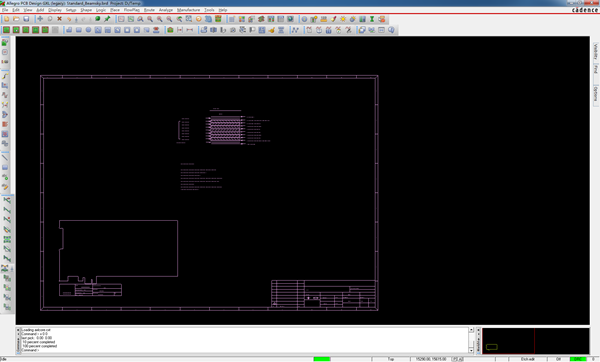

1. 使用Allegro打開上一代PCB文件,在顏色設(shè)置對話框中,關(guān)閉所有其他顏色,只保留Outline,如下圖。

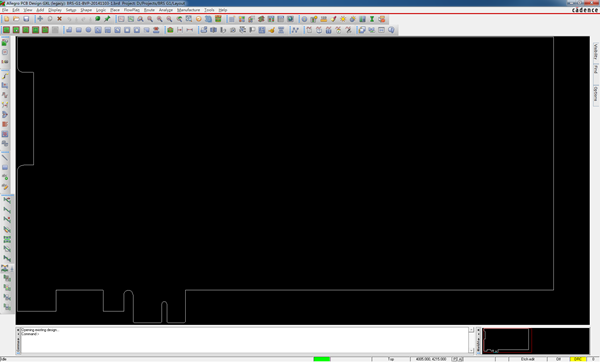

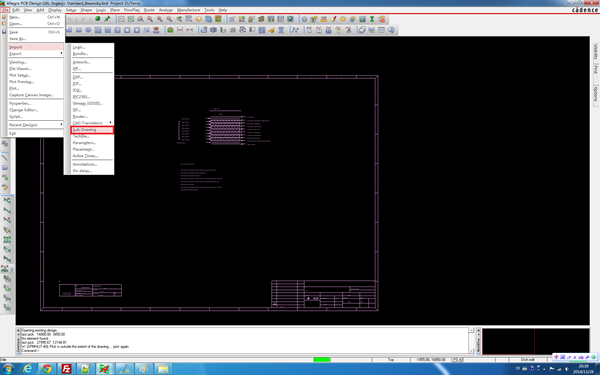

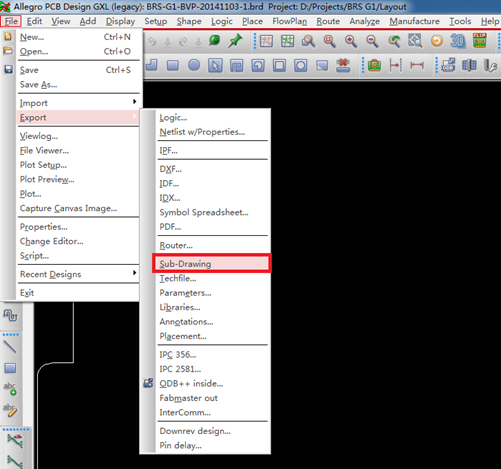

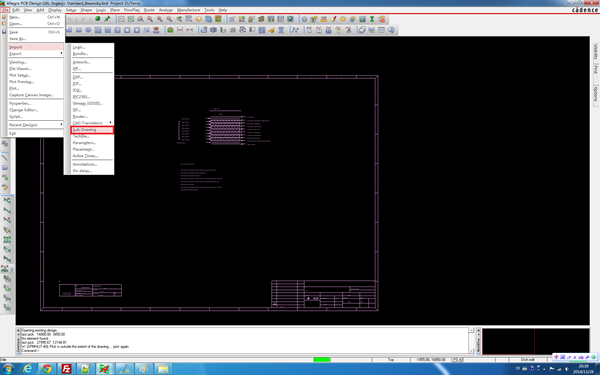

2. 點擊File—>Export—>Sub-Drawaing,如下圖。

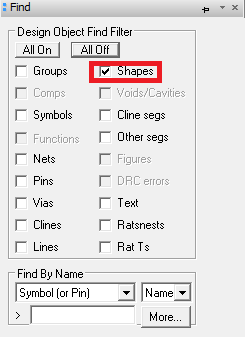

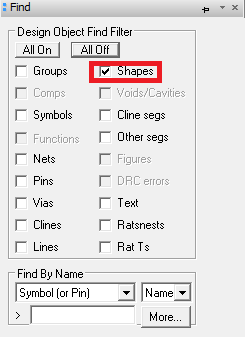

3. 在右側(cè)的Find中只勾選Shapes,如下圖。

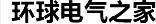

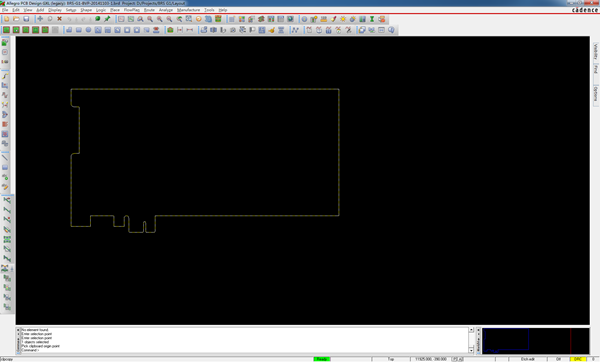

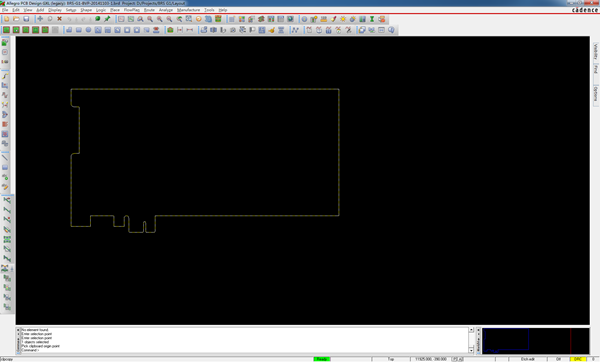

4. 用鼠標(biāo)圈住PCB外框,如下圖。

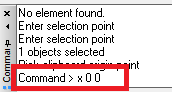

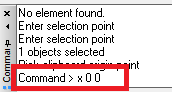

5. 在Command窗口中輸入“x 0 0”,注意此處區(qū)分大小寫,如下圖。

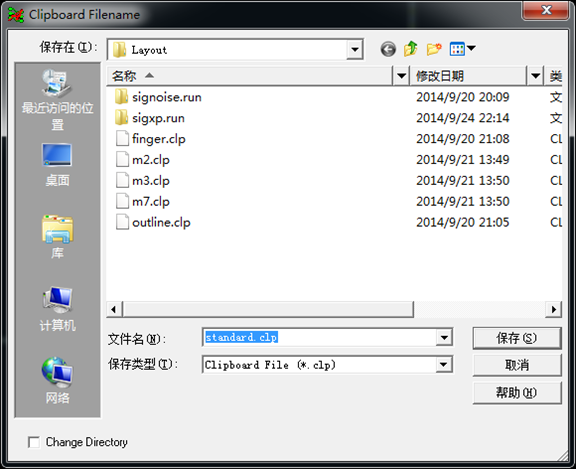

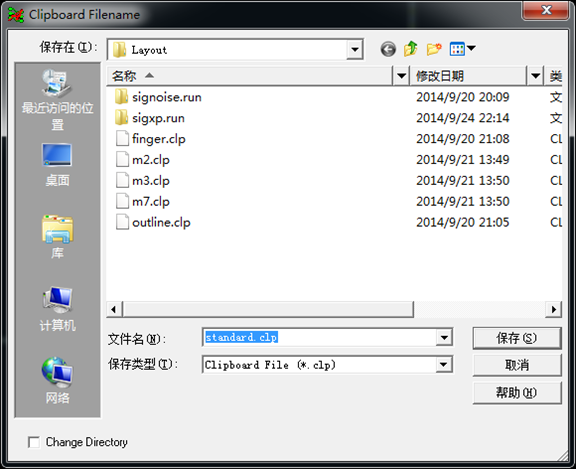

6. 在地5步基礎(chǔ)上敲回車,即可將僅包含Outline的Sub-Drawing保存,如下圖。Allegro默認將這個Sub-Drawing命名為“standard.clp”。

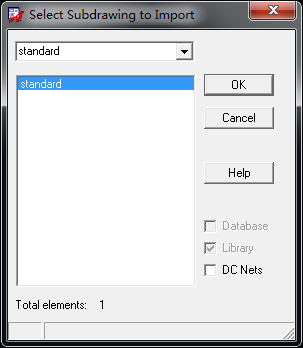

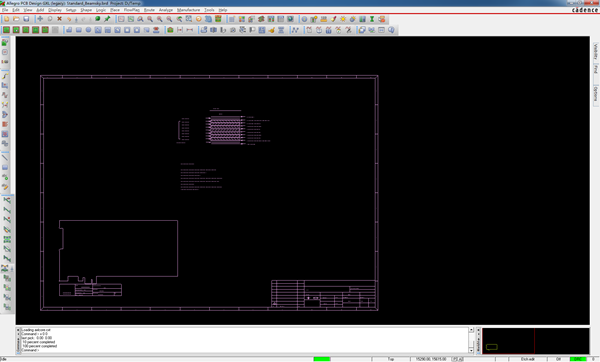

7. 將第6步中得到的standard.clp復(fù)制到新的PCB所在的目錄,本例中是D:Temp。打開一個新的PCB文件,并點擊File—>Import—>Sub-Drawing,如下圖。

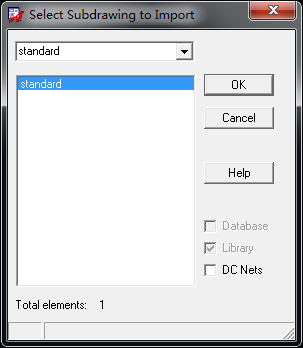

8. 在彈出的對話框中選擇standard.clp,然后點擊OK,如下圖。

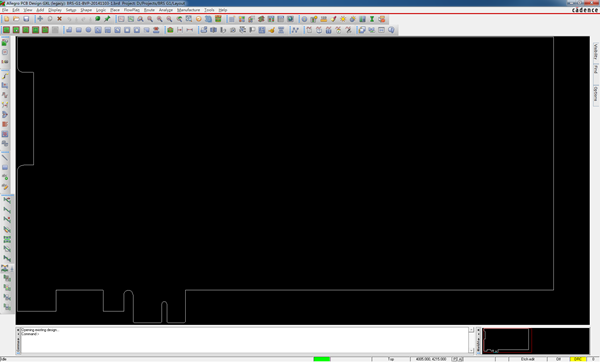

9. 與步驟5類似,在Command窗口中輸入“x 0 0”,注意此處區(qū)分大小寫。導(dǎo)入outline的最終效果如下圖類似。