Other Parts Discussed in Post: MSP430FR2311

作者: TI 工程師 Max Han

相關附件下載:5344.MSP430FR2311 中UART通訊的累積誤差分析計算.xlsx

簡介

在UART通訊設計中,工程師會根據(jù)系統(tǒng)需要先選定合適的波特率(Baud Rate),然后選擇合適的時鐘源頻率,以使UART傳輸數(shù)據(jù)時的累積誤差最小,數(shù)據(jù)的誤碼率最低。本文以MSP430FR2311為例,對UART數(shù)據(jù)傳輸過程中發(fā)送端累積誤差和接收端累積誤差進行了詳細的分析和計算。根據(jù)計算結(jié)果,工程師可以優(yōu)選出時鐘源頻率,提高UART數(shù)據(jù)傳輸系統(tǒng)的可靠性。

在附錄1的文章中,對MSP430FR2311的UART模塊寄存器配置的分析和計算有了詳細介紹,這里不再贅述。BRCLK是時鐘源頻率,BITCLK是波特率。當BRCLK是BITCLK的整數(shù)倍,即BRCLK/BITCLK=N,由于每個數(shù)據(jù)bit中含有N個BRCLK,和理想值完全相同,所以每個數(shù)據(jù)bit不存在時長誤差,因此在數(shù)據(jù)傳輸過程中也不存在累積誤差。但是大部分情況下BRCLK不是BITCLK的整數(shù)倍,由于在數(shù)據(jù)傳輸過程中,每個數(shù)據(jù)bit時長都是BRCLK的整數(shù)倍,這樣在每個數(shù)據(jù)bit中就存在時長誤差,因此在數(shù)據(jù)傳輸過程中也就存在累積誤差。

以下分4部分進行累積誤差的分析和計算:低頻波特率的發(fā)射端累積誤差,高頻波特率的發(fā)射端累積誤差,低頻波特率的接收端累積誤差,高頻波特率的接收端累積誤差。

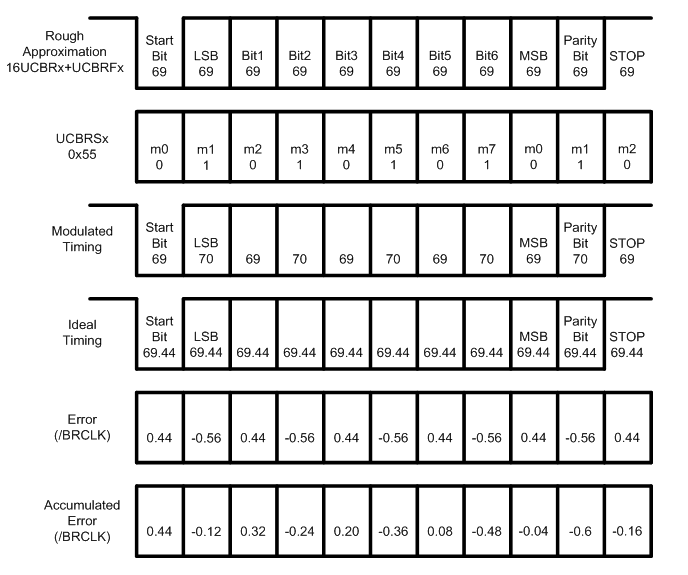

低頻波特率的發(fā)射端累積誤差

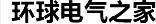

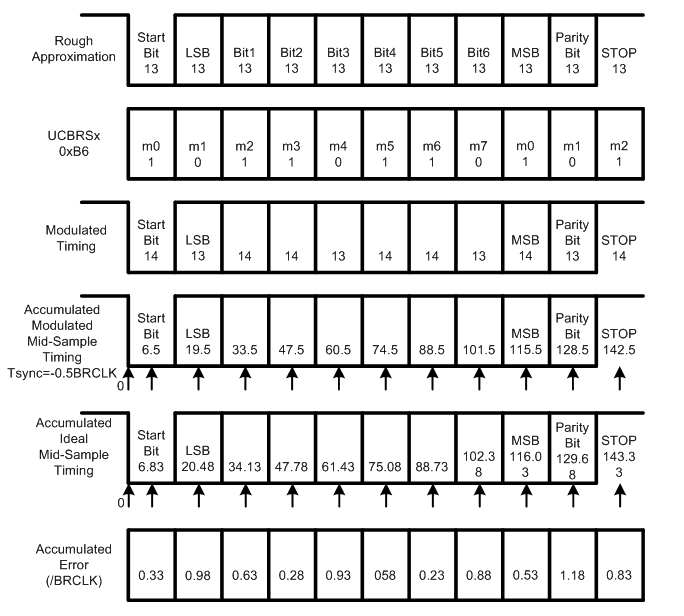

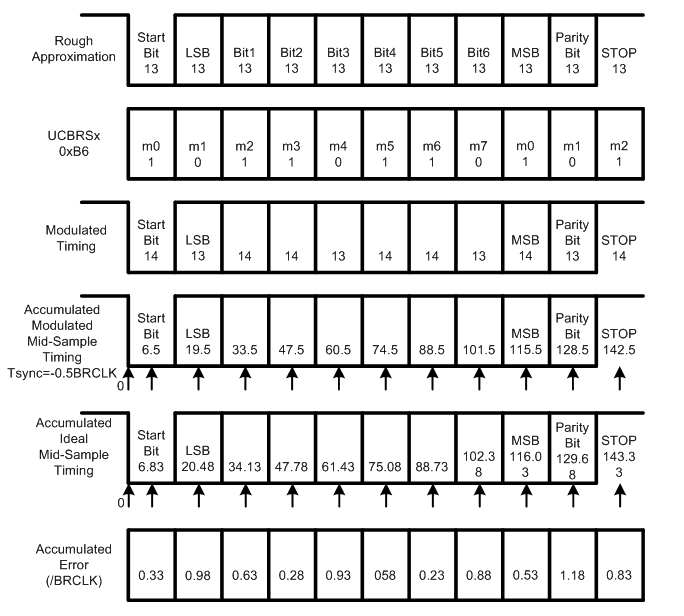

以時鐘源頻率BRCLK 32768Hz,波特率BITCLK 2400Hz為例,32768/2400=13.6533,所以UCOS16=0,UCBRx=13,UCBRSx=0xB6.

如圖1所示,在每個數(shù)據(jù)bit的發(fā)送結(jié)束時刻,實際發(fā)送時長和理想發(fā)送時長存在誤差。

對于Start bit,理想時長13.65BRCLK,實際時長14BRCLK,誤差時長為13.65BRCLK-14BRCLK=-0.35BRCLK。

對于LSB bit,理想時長13.65BRCLK,實際時長13BRCLK,誤差時長為13.65BRCLK-13BRCLK=0.65BRCLK,累積誤差時長為-0.35BRCLK+0.65BRCLK=0.30BRCLK。

對于Bit1,理想時長13.65BRCLK,實際時長14BRCLK,誤差時長為13.65BRCLK-14BRCLK=-0.35BRCLK,累積誤差時長為0.30BRCLK-0.35BRCLK=-0.05BRCLK。

后續(xù)bit位的誤差和累積誤差以此類推。

圖1低頻波特率的發(fā)射端累積誤差示意圖

以下是低頻波特率的發(fā)射端累積誤差的公式推導。

t_bits_ideal_TX為發(fā)送端理想累積數(shù)據(jù)時長。

t_bits_ideal_TX[i] = (i+1)/BITCLK (1)

t_bit_period_TX為發(fā)送端實際每個數(shù)據(jù)bit時長。每個數(shù)據(jù)的BRCLK個數(shù)等于UCBRx值和UCBRSx的對應調(diào)制值UCBRSx.m之和。

t_bit_period_TX[i] = (UCBRx +UCBRSx.m)/BRCLK (2)

t_bits_TX為發(fā)送端實際發(fā)送的累積數(shù)據(jù)時長。

t_bits_TX[0] = t_bit_period_TX[0] (3)

t_bits_TX[i] = t_bits_TX[i-1] + t_bit_period_TX[i], 其中i≠0 (4)

定義Error_TX為實際累積數(shù)據(jù)時長與理想累積數(shù)據(jù)時長的差值,相對于理想數(shù)據(jù)bit時長的百分比,單位為%

Error_TX[i]=( t_bits_ideal_TX[i]- t_bits_TX[i])*BITCLK*100 (5)

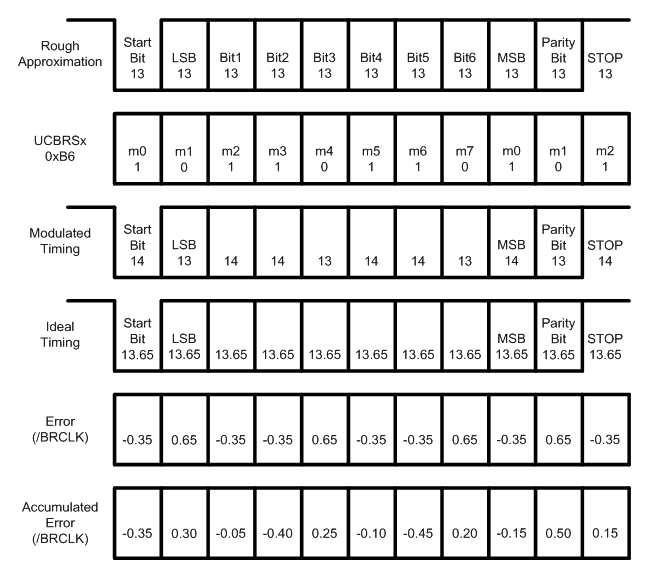

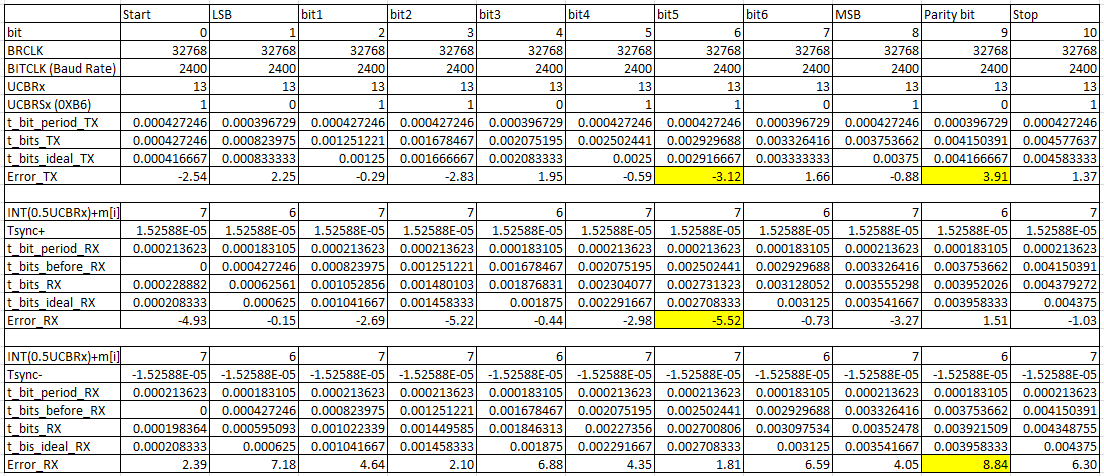

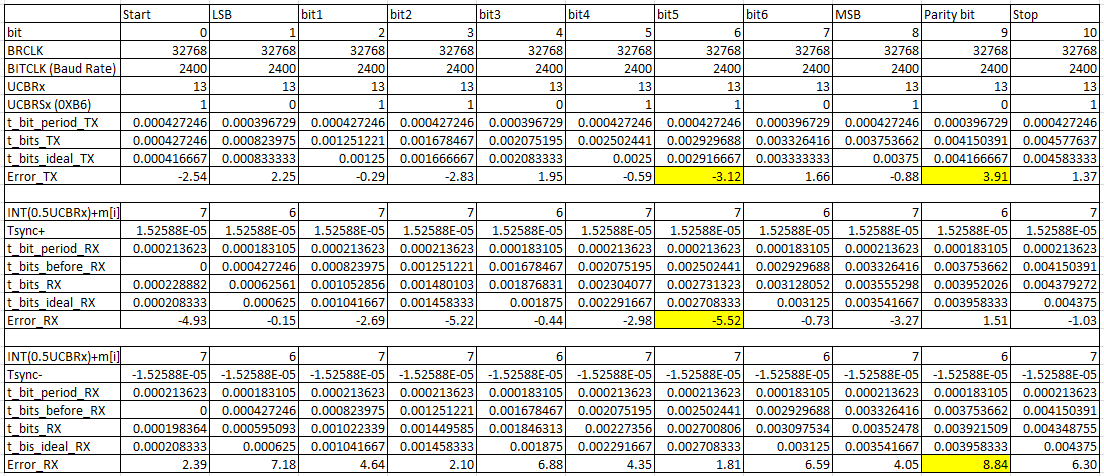

表1為帶入例程中數(shù)據(jù)的Error_TX的計算結(jié)果。

從表1中可以看到,最大正Error_TX為3.91%,最小負Error_TX為-3.12%.

表1 Error_TX

高頻波特率的發(fā)射端累積誤差

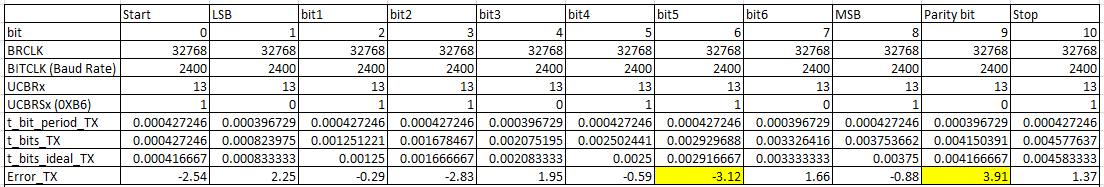

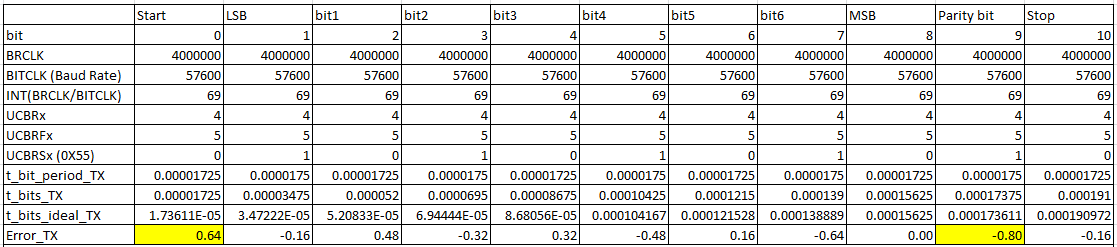

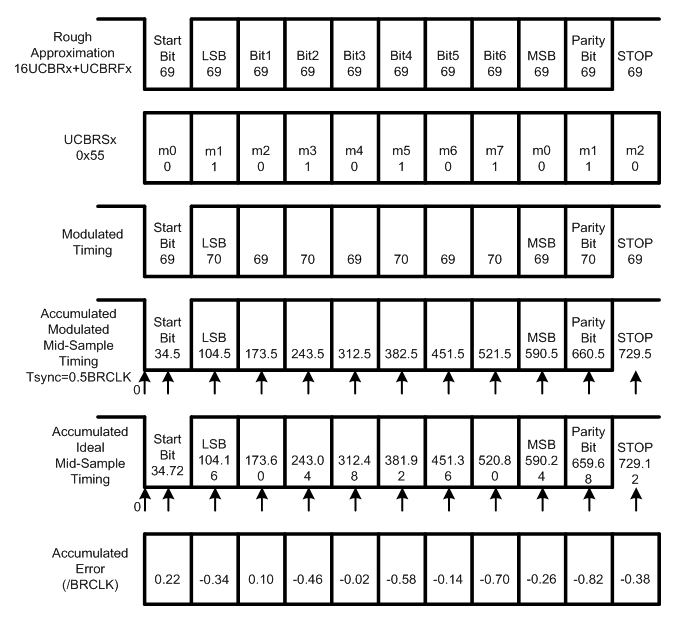

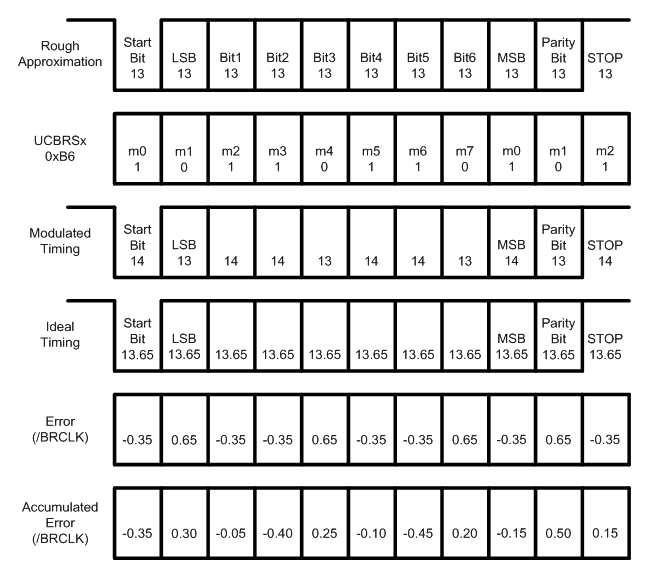

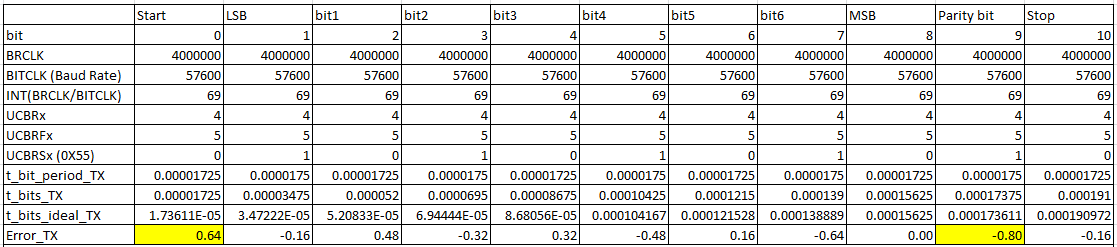

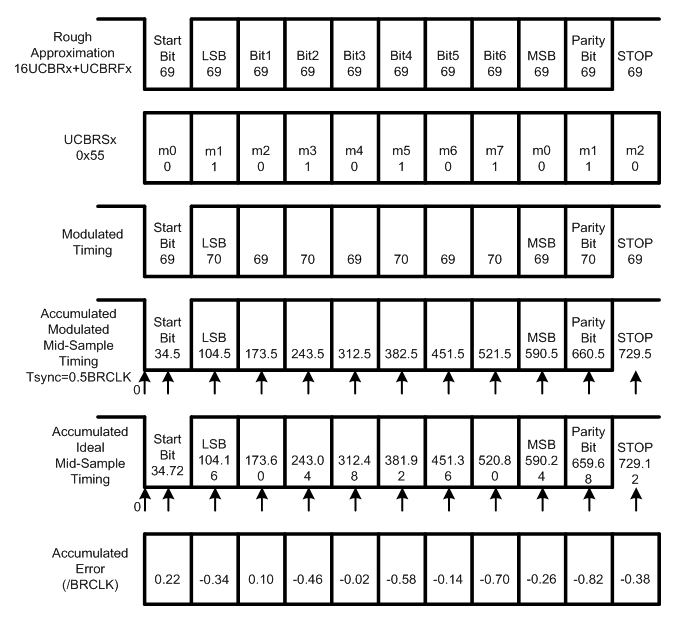

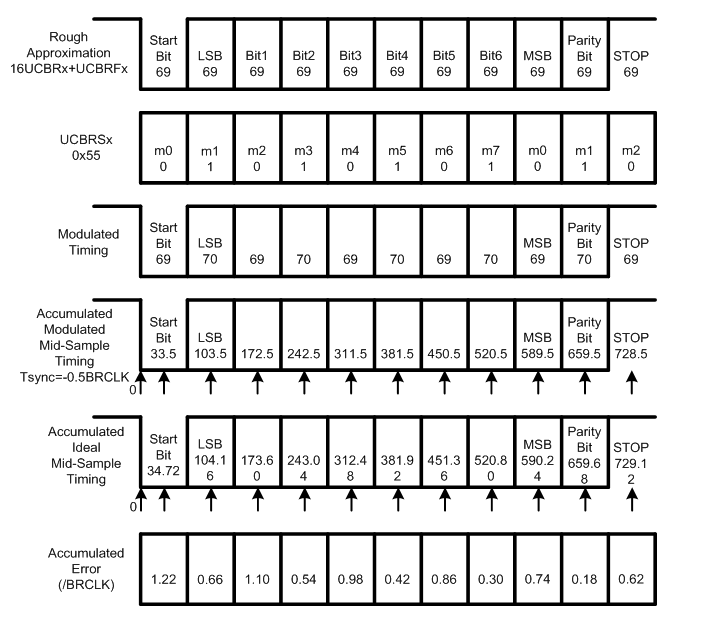

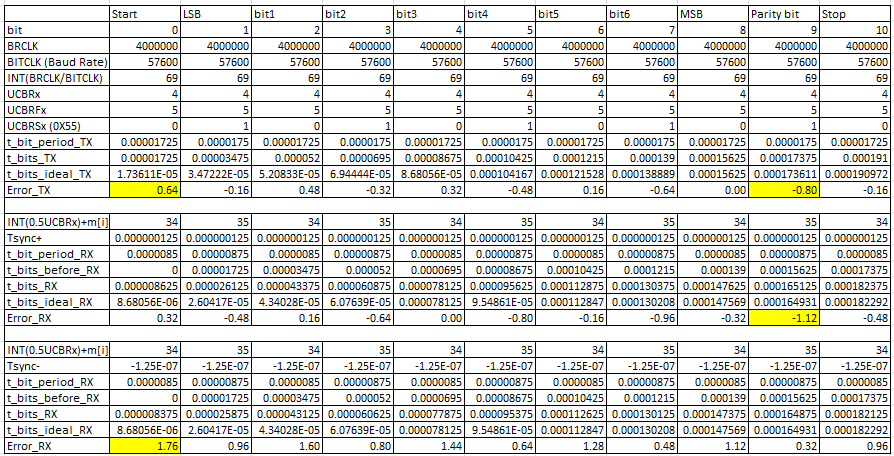

以時鐘源頻率BRCLK 4000000Hz,波特率BITCLK 57600為例,4000000/57600=69.4444,所以UCOS16=1,UCBRx=4,UCBRFx=5,UCBRSx=0x55.

如圖2所示,在每個數(shù)據(jù)bit的發(fā)送結(jié)束時刻,實際發(fā)送時長和理想發(fā)送時長存在誤差。

對于Start bit,理想時長69.44BRCLK,實際時長69BRCLK,誤差時長為69.44BRCLK-69BRCLK=0.44BRCLK。

對于LSB bit,理想時長69.44BRCLK,實際時長70BRCLK,誤差時長為69.44BRCLK-70BRCLK=-0.56BRCLK,累積誤差時長為0.44BRCLK-0.56BRCLK=-0.12BRCLK。

對于Bit1,理想時長69.44BRCLK,實際時長69BRCLK,誤差時長為69.44BRCLK-69BRCLK=0.44BRCLK,累積誤差時長為-0.12BRCLK+0.44BRCLK=0.32BRCLK。

后續(xù)bit位的誤差和累積誤差以此類推。

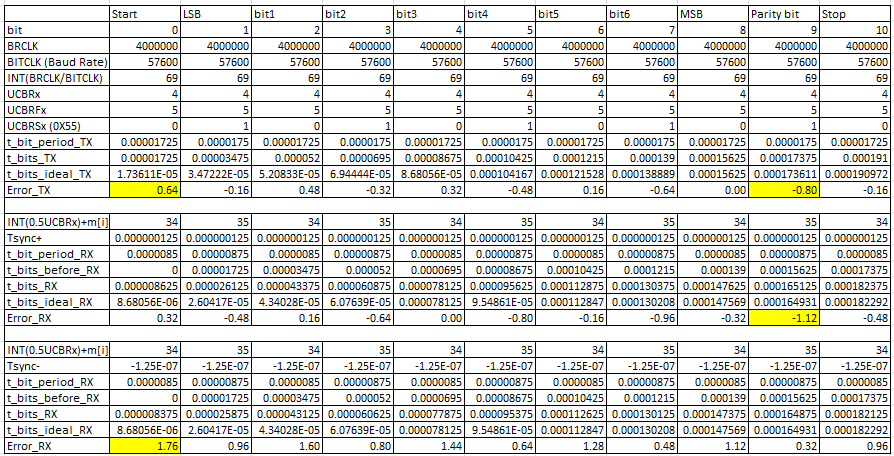

圖2高頻波特率的發(fā)射端累積誤差示意圖

以下是高頻波特率的發(fā)射端累積誤差的公式推導。

t_bits_ideal_TX為發(fā)射端理想累積數(shù)據(jù)時長。

t_bits_ideal_TX[i] = (i+1)/BITCLK (6)

t_bit_period_TX為發(fā)射端實際每個數(shù)據(jù)bit時長。每個數(shù)據(jù)的BRCLK個數(shù)等于16*UCBRx+UCBRFx值和UCBRSx的對應調(diào)制值UCBRSx.m之和。

t_bit_period_TX[i] = (16*UCBRx+UCBRFx +UCBRSx.m)/BRCLK (7)

t_bits_TX為發(fā)射端實際發(fā)送的累積數(shù)據(jù)時長。

t_bits_TX[0] = t_bit_period_TX[0] (8)

t_bits_TX[i] = t_bits_TX[i-1] + t_bit_period_TX[i], 其中i≠0 (9)

定義Error_TX為實際累積數(shù)據(jù)時長與理想累積數(shù)據(jù)時長的差值,相對于理想數(shù)據(jù)bit時長的百分比,單位為%

Error_TX[i]=( t_bits_ideal_TX[i]- T_bits_TX[i])*BITCLK*100 (10)

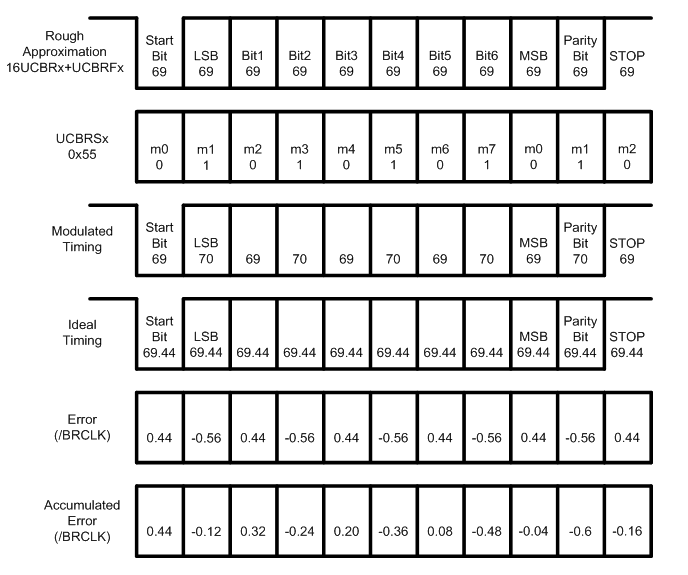

表2為帶入例程中數(shù)據(jù)的Error_TX的計算結(jié)果。

從表2中可以看到,最大正Error_TX為0.64%,最小負Error_TX為-0.80%.

表2 Error_TX

低頻波特率的 接收端累積誤差

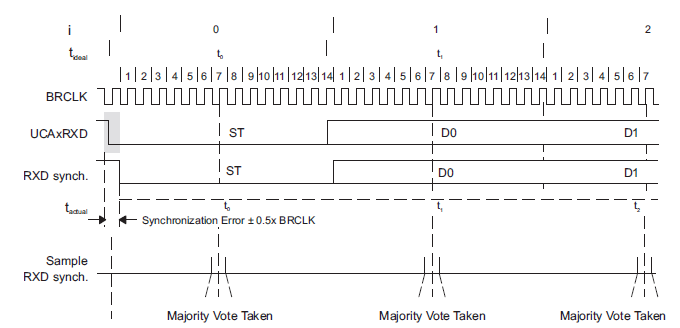

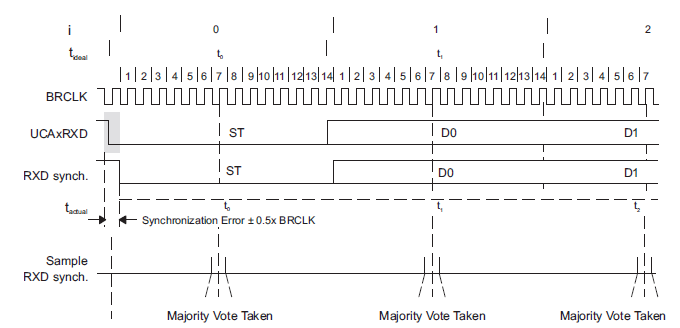

MSP430FR2311 User’s Guide中指出,接收端誤差包括兩部分:一個是從發(fā)射端start bit開始邊沿到該邊沿被接收端識別的誤差,另一個是每個數(shù)據(jù)bit實際識別時刻和理想識別時刻的偏差。如圖3所示。

圖3 接收端兩種誤差

第一種誤差用Tsync表示,Tsync = ±0.5BRCLK。

對于第二種誤差,由于理想情況下接收端是在數(shù)據(jù)bit時長一半的位置進行采樣識別,所以在進行誤差計算時,是以該時刻為參考進行計算,而不像發(fā)射端,是以該數(shù)據(jù)bit理想時長結(jié)束的位置為參考進行計算。

MSP430FR2311 User’s Guide中給出了計算公式,但是這些公式中包含的元素太多不便理解。本文通過簡化的方式來進行理解和計算,可以得到相同的累積誤差結(jié)果。

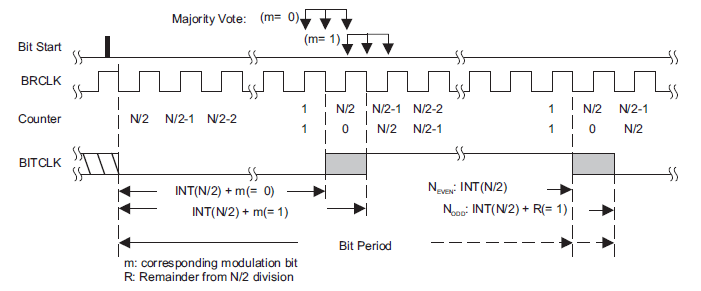

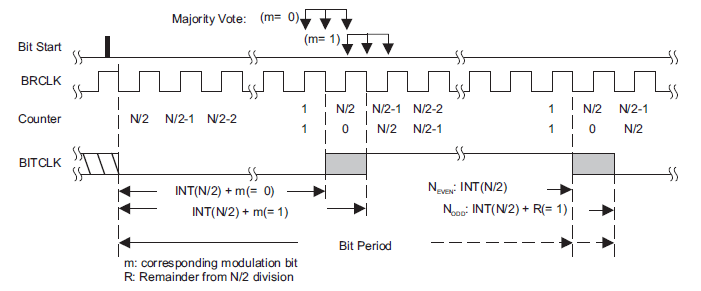

圖4為MSP430FR2311的Majority Vote示意圖,從圖中可以看出Majority Vote在三個邊沿的位置進行數(shù)據(jù)采樣,采樣的中心位置為INT(N/2)+m,其中N=INT(BRCLK/BITCLK), m為UCBRSx中對應于該數(shù)據(jù)bit的UCBRSx.m值。理想的數(shù)據(jù)bit采樣中心位置為0.5/BITCLK。

圖4 Majority Vote示意圖

所以對于從Start bit開始的第i個數(shù)據(jù)bit,其采樣中心位置時刻為Tsync,前i-1個數(shù)據(jù)bit實際總時長和該數(shù)據(jù)bit采樣中心位置時長的總和,然后和理想的第i個數(shù)據(jù)bit采樣中心位置時刻進行比較,便可得出第i個數(shù)據(jù)bit的累積誤差。

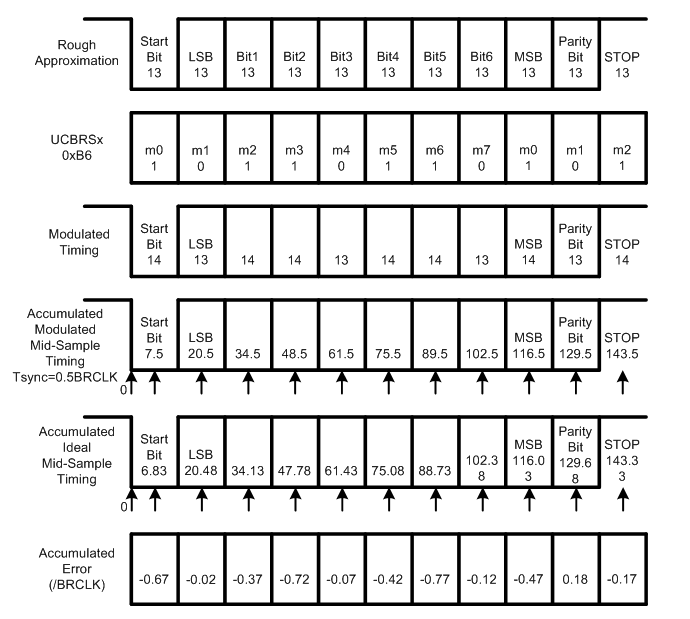

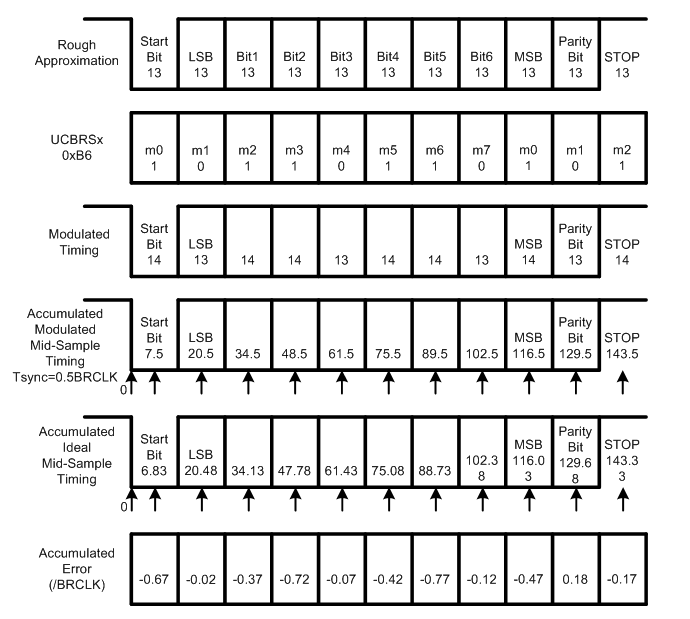

以時鐘源頻率BRCLK 32768Hz,波特率BITCLK 2400Hz為例,32768/2400=13.6533,所以UCOS16=0,UCBRx=13,UCBRSx=0xB6.理想數(shù)據(jù)bit采樣中心位置13.6533/2=6.8267BRCLK。

如圖5和圖6所示,在每個數(shù)據(jù)bit采樣中心位置時刻,實際累積采樣時刻和理想累積采樣時刻存在誤差。

當考慮Tsync=0.5BRCLK時,如圖5所示。

對于Start bit,理想數(shù)據(jù)bit累積采樣中心位置時刻為6.83BRCLK,實際數(shù)據(jù)bit累積采樣中心位置時刻為7.5BRCLK,誤差為6.83BRCLK-7.5BRCLK=-0.67BRCLK。

對于LSB bit,理想數(shù)據(jù)bit累積采樣中心位置時刻為20.48BRCLK,實際數(shù)據(jù)bit累積采樣中心位置時刻為20.5BRCLK,誤差為20.48BRCLK-20.5BRCLK=-0.02BRCLK。

對于Bit1,理想數(shù)據(jù)bit累積采樣中心位置時刻為34.13BRCLK,實際數(shù)據(jù)bit累積采樣中心位置時刻為34.5BRCLK,誤差為34.13BRCLK-34.5BRCLK=-0.37BRCLK。

后續(xù)bit位的累積誤差以此類推。

當考慮Tsync=-0.5BRCLK時,如圖6所示。

分析方法和圖5一樣,不再贅述。

圖5低頻波特率的接收端累積誤差示意圖,Tsync=0.5BRCLK

圖6低頻波特率的接收端累積誤差示意圖,Tsync=-0.5BRCLK

以下是低頻波特率的接收端累積誤差的公式推導。

t_bits_ideal_RX為接收端理想數(shù)據(jù)bit累積采樣中心位置時刻。

t_bits_ideal_RX[i] = (i+0.5)/BITCLK (11)

t_bit_period_RX為接收端實際數(shù)據(jù)bit采樣中心位置時刻。每個數(shù)據(jù)bit采樣中心位置時刻的BRCLK個數(shù)等于INT(0.5UCBRx)和UCBRSx的對應調(diào)制值UCBRSx.m之和。

t_bit_period_RX[i] = [INT(0.5*UCBRx) +UCBRSx.m]/BRCLK (12)

t_bits_before_RX為當前數(shù)據(jù)bit之前的所有i-1個數(shù)據(jù)bit實際累積數(shù)據(jù)時長。

t_bits_before_RX[0] = 0

t_bits_before_RX[i] = t_bits_before_RX[i-1] + (UCBRx[i-1] + UCBRSx.m[i-1])/BRCLK, 其中i≠0 (13)

其中t_bits_before_RX[i-1]為所有i-2個數(shù)據(jù)bit實際累積數(shù)據(jù)時長,(UCBRx[i-1] + UCBRSx.m[i-1])/BRCLK為第i-1個數(shù)據(jù)bit實際數(shù)據(jù)時長。

t_bits_RX為接收端實際數(shù)據(jù)bit累積采樣中心位置時刻。

t_bits_TX[i] = Tsync + t_bit_period_RX[i] + t_bits_before_RX[i] (14)

定義Error_TX為接收端實際數(shù)據(jù)bit累積采樣中心位置時刻相對于理想數(shù)據(jù)bit累積采樣中心位置時刻的誤差占理想數(shù)據(jù)bit時長的百分比,單位為%

Error_TX[i]=( t_bits_ideal_TX[i]- T_bits_TX[i])*BITCLK*100 (15)

表3為帶入例程中數(shù)據(jù)的Error_TX。

從表3中可以看到,最大正Error_TX為8.84%,最小負Error_TX為-5.52%.

表3 Error_TX

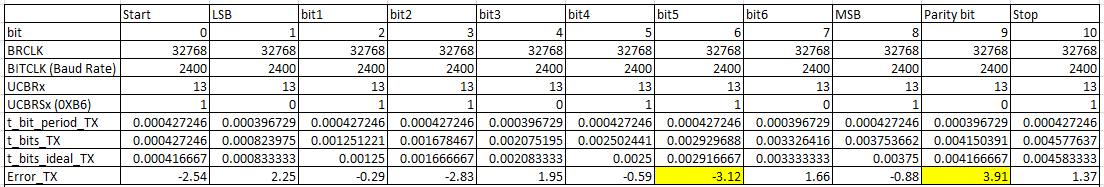

高頻波特率的 接收端累積誤差

以時鐘源頻率BRCLK 4000000Hz,波特率BITCLK 57600為例,4000000/57600=69.4444,所以UCOS16=1,UCBRx=4,UCBRFx=5,UCBRSx=0x55. 理想數(shù)據(jù)bit采樣中心位置69.4444/2=34.7222BRCLK.

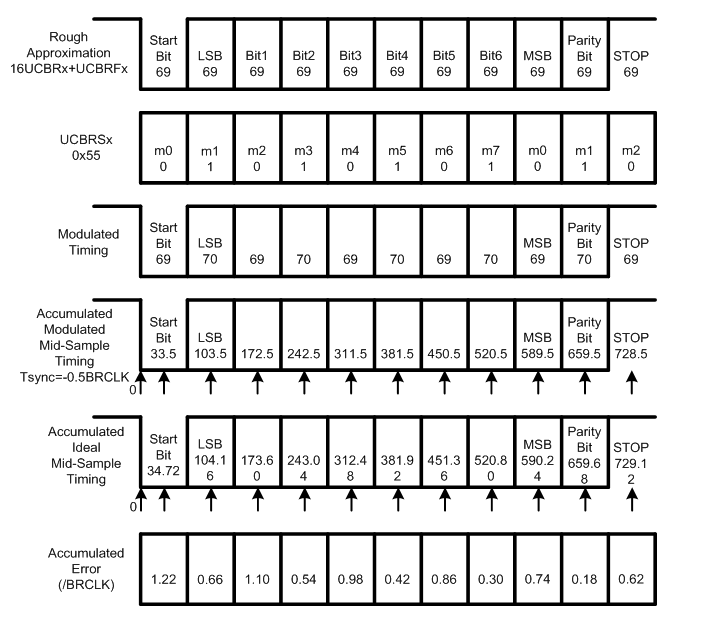

如圖7和圖8所示,在每個數(shù)據(jù)bit累積采樣中心位置時刻,實際采樣時刻和理想采樣時刻存在誤差。

當考慮Tsync=0.5BRCLK時,如圖7所示。

對于Start bit,理想數(shù)據(jù)bit累積采樣中心位置時刻為34.72BRCLK,實際數(shù)據(jù)bit累積采樣中心位置時刻為34.5BRCLK,誤差為34.72BRCLK-34.5BRCLK=0.22BRCLK。

對于LSB bit,理想數(shù)據(jù)bit累積采樣中心位置時刻為104.16BRCLK,實際數(shù)據(jù)bit累積采樣中心位置時刻為104.5BRCLK,誤差為104.16BRCLK-104.5BRCLK=-0.34BRCLK。

對于Bit1,理想數(shù)據(jù)bit累積采樣中心位置時刻為173.60,實際數(shù)據(jù)bit累積采樣中心位置時刻為173.5BRCLK,誤差為173.60BRCLK-173.5BRCLK=0.10BRCLK。

后續(xù)bit位的累積誤差以此類推。

當考慮Tsync=-0.5BRCLK時,如圖8所示。

分析方法和圖7一樣,不再贅述。

圖7高頻波特率的接收端累積誤差示意圖,Tsync=0.5BRCLK

圖8高頻波特率的接收端累積誤差示意圖,Tsync=-0.5BRCLK

以下是高頻波特率的接收端累積誤差的公式推導。

t_bits_ideal_RX為接收端理想數(shù)據(jù)bit累積采樣中心位置時刻。

t_bits_ideal_RX[i] = (i+0.5)/BITCLK (16)

t_bit_period_RX為接收端實際數(shù)據(jù)bit采樣中心位置時刻。每個數(shù)據(jù)bit采樣中心位置時刻的BRCLK個數(shù)等于INT[0.5*(16*UCBRx+UCBRFx)]和UCBRSx的對應調(diào)制值UCBRSx.m之和。

t_bit_period_RX[i] = [INT(0.5*(16*UCBRx+UCBRFx)) +UCBRSx.m]/BRCLK (17)

t_bits_before_RX為當前數(shù)據(jù)bit之前的所有i-1個數(shù)據(jù)bit實際累積數(shù)據(jù)時長。

t_bits_before_RX[0] = 0

t_bits_before_RX[i] = t_bits_before_RX[i-1] + (16*UCBRx+UCBRFx + UCBRSx.m)/BRCLK, 其中i≠0 (18)

其中t_bits_before_RX[i-1]為所有i-2個數(shù)據(jù)bit實際累積數(shù)據(jù)時長,(16*UCBRx+UCBRFx + UCBRSx.m)/BRCLK為第i-1個數(shù)據(jù)bit實際數(shù)據(jù)時長。

t_bits_RX為接收端實際數(shù)據(jù)bit累積采樣中心位置時刻。

t_bits_TX[i] = Tsync + t_bit_period_RX[i] + t_bits_before_RX[i] (19)

定義Error_TX為接收端實際數(shù)據(jù)bit累積采樣中心位置時刻相對于理想數(shù)據(jù)bit累積采樣中心位置時刻的誤差占理想數(shù)據(jù)bit時長的百分比,單位為%

Error_TX[i]=( t_bits_ideal_TX[i]- T_bits_TX[i])*BITCLK*100 (20)

表4為帶入例程中數(shù)據(jù)的Error_TX。

從表4中可以看到,最大正Error_TX為1.76%,最小負Error_TX為-1.12%.

表4 Error_TX

時鐘源頻率優(yōu)選

時鐘源頻率優(yōu)選需要考慮兩方面的因素:

盡量降低發(fā)射端累積誤差和接收端累積誤差

對于Majority Vote架構,過高的時鐘源頻率會減小Majority Vote的檢測窗口,降低Majority Vote的性能

以波特率9600Hz為例, Error_TX和Error_RX如表5所示,根據(jù)時鐘源優(yōu)選原則,選擇1000000Hz。

表5 Error_TX和Error_RX

BRCLK | BITCLK | Error_TX+ (%) | Error_TX- (%) | Error_RX+ (%) | Error_RX- (%) |

32768 | 9600 | 16.02 | -17.19 | 37.30 | -23.24 |

1000000 | 9600 | 0.64 | -0.48 | 1.04 | -1.04 |

8000000 | 9600 | 0.04 | -0.08 | 0.14 | -0.10 |

參考文獻

1. MSP430FR2311 中UART模塊寄存器配置的分析和計算,Max Han

2. MSP430FR4xx and MSP430FR2xx Family User's Guide,SLAU445H