本文介紹了基于FPGA技術對嵌入式SoC系統進行在線監控的方法。設計了一個FPGA片上通信系統,該系統內部固化基于UART接口的Modbus通訊協議棧,可通過串口與PC上位機進行通信;且采用雙口RAM作為與監控對象間共享的數據緩存區,通過中斷機制實現數據的同步交換,既確保了監控數據的實時性,也避免了嵌入式系統因處理監控通信過程而帶來性能損失。采用VHDL語言設計實現了通信系統的各組成部分,在Altera的cycloneII系列芯片開發板上驗證了方案的可行性。 在SoC系統的設計及使用過程中,對其內部行為的實時監控十分重要,目前普遍通過監控端和目標系統間的監控信息通信來實現,UART常用作通信信道。目標SoC系統常使用中斷方式或輪詢方式獲取監控通信數據包,對其解析并進行相應數據操作后回復應答信息。中斷方式中SoC需完成保存中斷現場、調用中斷服務程序、恢復現場系列任務,上下文的切換占據了系統額外開銷;輪詢方式中,系統定時檢查設備請求,若有數據到達則調用相應處理程序,固定的輪詢周期增加了數據等待處理時間,數據量較小時頻繁查詢造成對CPU資源的浪費。 針對上述問題,提出一種的新監控方法,設計一個FPGA通信系統,由其作為SoC與監控計算機數據交互的橋梁,負責完成在線監控的通信過程,保證被調試系統和調試主機之間調試信息和命令的交互可靠性,可避免目標SoC頻繁的處理通信中斷,提高其控制性能。監控功能實現機制與通信系統主要模塊的設計方法將被討論,通過對比嵌入式CPU在不同監控方法中的通信時間消耗,說明該方法具有一定實用價值。

1 系統組成結構

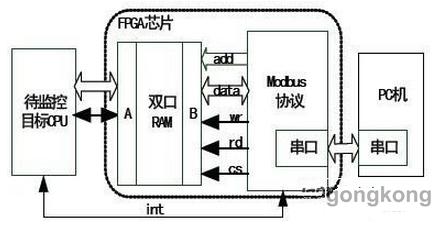

基于FPGA設計片上通信系統如圖1所示,其主要組成部分為Modbus解析模塊和雙口RAM存儲模塊。上位機發出監控命令幀數據時,由Modbus模塊完成命令幀的接收、解析過程,并將待操作地址、數據等信息存入雙口RAM中,目標CPU據此將自身內存映像區的相應數據一次搬入雙口RAM,搬移完畢后,Modbus協議模塊進行應答數據組幀,并向監控上位機發回應答數據,實現對監控數據的實時可靠采集。

圖 1 通信系統組成結構

2 基于雙口RAM的數據交互設計

2.1 雙口RAM定制及內存映射設計

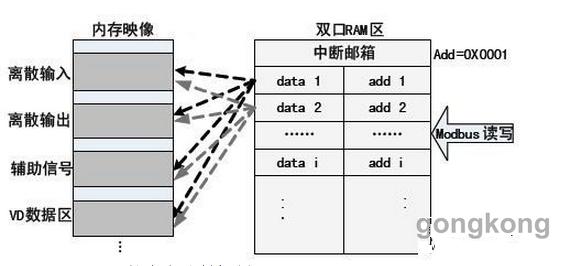

目標SoC中的待監控數據狀態量在內存中的存儲方式,可抽象表示為如圖2中內存映像。

圖 2 雙口 RAM 的內存映射機制

雙口RAM中存儲當前待監控數據對象集合,是目標CPU內存映像區的一個數據子集。由于當前監控對象可隨機落在內存映像區的任意存儲塊上,雙口RAM的內存映射方式選取為隨機映射,如圖2所示。

分散存放于CPU內存映像區的監控對象,映射為雙口RAM中的連續存儲區。上位機基于Modbus協議與FPGA片上系統通信時,訪問連續的地址單元,保證了數據訪問速度,提高系統的通信效率。

2.2 雙口RAM中的數據操作設計

2.2.1 上位機對雙口RAM的讀寫操作

PC上位機為通信發起方,通過串口與FPGA片上系統連接,采用Modbus-RTU協議進行數據通信,完成對運行參數的讀取和寫入等操作,實現監控功能。

表 1 監控通信過程占用 CPU 時間

用戶在人機界面輸入本次待監控對象信息, 后臺軟件依據Modbus幀結構及約定的雙口RAM內存映射機制,組成監控命令幀并通過串口發出。FPGA片上系統對收到的命令幀進行解析,獲取操作功能碼、目標地址、數據包大小等信息,據此向雙口RAM區寫入待操作數據地址集,寫入完畢后向目標CPU申請通信中斷。根據Modbus命令幀中給出的數據操作長度,一次可對多個數據單元進行讀/寫操作。

2.2.2 目標CPU對雙口RAM的讀寫操作

目標CPU收到通信中斷請求后,讀雙口RAM區的中斷郵箱,郵箱信息包含本次申請功能(讀或寫)及申請的數據項個數等。根據申請地址集,將自身內存映像區相應數據集一次搬入雙口RAM,或將雙口RAM中數據集一次搬入內存映像區相應地址處,搬移完畢后,清空中斷郵箱,向監控模塊發出中斷應答。

3 Modbus協議棧模塊的設計與實現

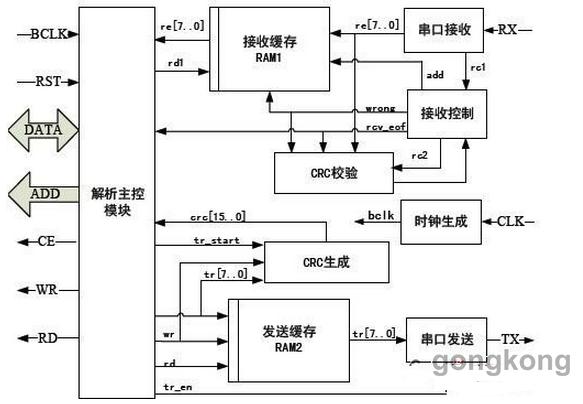

采用自頂向下的設計方法,根據功能需求設計Modbus協議棧頂層原理框圖如圖3。使用VHDL硬件描述語言編程實現各組成子模塊,功能如下述。

圖 3 Modbus 協議棧頂層框圖

(1)時鐘生成模塊:通過分頻和相移產生位時鐘clk和1/16位時鐘bclk,作為控制其他模塊的運行節拍,保證系統運行同步。

(2)串口接收模塊:以bclk作為控制時鐘,對接收的位數據作中點采樣,進行串并裝換得到字節數據。

(3)串口發送模塊:以bclk作為控制時鐘,發送使能信號有效時,輸入端的字節數據進行并串裝換,通過串口發出。

(4)接收控制模塊:判斷幀的起始、結束、是否接收錯誤;提供地址數據,接收的字節數據被存儲至RAM1中相應存儲單元。

(5)CRC校驗/生成模塊:使用基于字節的CRC_16校驗碼運算方法。接收端的校驗過程與數據接收同步進行,接收控制模塊每收到一個字節數據,CRC校驗模塊對其作一次CRC碼計算;CRC生成模塊運行機制類同。同步運算可有效減少一次對幀數據的遍歷。

(6)解析主控模塊:作為系統的核心,負責解析收到的命令幀,根據解析信息進行數據讀寫操作,組成應答幀,控制串口發送模塊發送應答數據等多項任務。收到一個校驗無誤的命令幀后,控制讀取接收緩存區RAM1中數據,比照Modbus幀格式解析命令幀含義,通過對外數據、地址等接口完成對雙口RAM的讀寫操作;解析及操作完畢后,控制應答幀組幀過程,將應答數據依次寫入RAM2發送緩存區,全部寫入后,將CRC生成模塊中CRC_16校驗值按低位在前高位在后順序,依次存放到發送緩存的下兩個地址位置處,此時應答幀準備完畢;控制發出應答幀,依次讀取出發送緩存區數據(讀脈沖間的時間間隔至少大于串口發送單個字節所需時間),每取出一個數據,提供發送使能脈沖供串口發送模塊工作,脈寬等于串口發送單個字節所需時間,直至應答幀全部發送完畢。

(7)接收緩存RAM1/發送緩存RAM2:存儲串口接收模塊收到的字節數據/存儲待發送的應答幀。

4 性能分析 分析監控通信對Soc系統性能的影響,設定一系列參數如下:時間基數T(min)、監控頻率m(幀/min)、監控命令幀平均長度n(byte/幀)、Soc主循環平均周期k(ms)、通信波特率B(bit/s)、中斷處理指令數r(條)、查詢語句指令數s(條)、處理器主頻f(HZ)。針對常用的輪詢監控、中斷監控,及該文所提出的基于FPGA的DRAM監控方法,可按照表1公式計算其監控通信過程占用的CPU時間。對于常用ARM處理器,可例舉部分參數值f=72M,r=15,s=5。設定其余參數值T=1,m=100,n=30,k=0.05,B=115200。在當前設定下,計算得出三種監控方法對CPU的時間占用百分比,如表1所示。對比應用單一的中斷或輪詢方式,使用該文提出的監控方法時,嵌入式系統CPU的利用率得到了明顯的提高。 5 結語 該文提出一種針對嵌入式片上系統的在線監控方法。利用FPGA技術設計了輔助監控系統,由該系統完成監控通信過程中的接收通信命令幀、解析命令幀及組成應答數據幀等任務,加快了對通信數據的處理速度。SoC有效減少了處理監控所需時間,更集中于其控制功能的執行,從而獲得更高的實時性。設計工作在Altera公司的QuartusII開發平臺上采用VHDL語言完成,使用CycoloneII系列芯片作功能驗證,通信系統的Modbus接口與上位機在115200的波特率下收發正確,雙口RAM內數據交互穩定,達到了預計效果。 |